# EFFICIENT VERIFICATION OF MULTI-PROCESSOR REAL-TIME SYSTEMS USING SYMBOLIC METHODS

Ву

Jason M. Scott

Dissertation

Submitted to the Faculty of the

Graduate School of Vanderbilt University

in partial fulfillment of the requirements

for the degree of

DOCTOR OF PHILOSOPHY

in

**ELECTRICAL ENGINEERING**

August, 2003

Nashville, Tennessee

| Approved: | Date: |

|-----------|-------|

|           |       |

|           |       |

|           |       |

|           |       |

|           |       |

|           |       |

© Copyright by Jason Matthew Scott, 2003

All Rights Reserved

#### **ACKNOWLEDGEMENTS**

Most of all I want to thank my wife, Amy, for her constant support and motivation. I would not have continued this dissertation if it were not for her support. She had to endure many nights alone so that I could complete this work and I cannot thank her enough. I would like to thank my family for their encouragement and for always being there when I needed them.

I am very appreciative of my advisor, Dr. Gabor Karsai, for his advice, technical feedback and encouragement (and much patience!). I would like to thank all the people who have helped me during my time as a graduate student at Vanderbilt. ISIS is composed of a friendly and knowledgeable group of people who have been great to work with. I would especially like to thank Dr. Ted Bapty for funding support and the interesting projects that I have had an opportunity to work on. I would also like to thank Dr. Richard Davis, Dr. Sandeep Neema, Dr. Greg Nordstrom and Brandon Eames for their friendship and encouragement. I have learned a lot from working with these guys in my time at Vanderbilt. Thanks also to the other members of my committee: Dr. Janos Sztipanovits, Dr. Vijay Raghavan, Dr. Bharat Bhuva, and Dr. Benoit Dawant.

# TABLE OF CONTENTS

|                                         | Page |

|-----------------------------------------|------|

| ACKNOWLEDGEMENTS                        | iii  |

| LIST OF TABLES                          | vii  |

| LIST OF FIGURES                         | viii |

| LIST OF ALGORITHMS                      | X    |

| Chapter                                 |      |

| I. INTRODUCTION                         | 1    |

| Overview                                | 6    |

| II. BACKGROUND AND RELATED APPROACHES   | 7    |

| Formal Verification.                    | 7    |

| Theorem Proving                         |      |

| Model Checking                          |      |

| Symbolic Model Checking                 |      |

| Symbolic Representations.               |      |

| Ordered Binary Decision Diagrams        |      |

| MTBDDs                                  |      |

| OBDD implementations                    |      |

| Model Checking Tools.                   |      |

| SMV                                     |      |

| Verus                                   |      |

| UPPAAL                                  |      |

| KRONOS                                  |      |

| Summary                                 | 33   |

| III. MODELS OF COMPUTATION              | 35   |

| Finite State Machines                   | 35   |

| Statecharts                             | 36   |

| RScharts                                | 39   |

| Syntax                                  | 39   |

| Step Semantics                          |      |

| Timed Automata                          | 46   |

| Timed Restricted Statechart (TRScharts) | 47   |

|     | Dataflow Models                                                                                       | 50  |

|-----|-------------------------------------------------------------------------------------------------------|-----|

|     | Dataflow Process Networks                                                                             | 50  |

|     | Synchronous Dataflow                                                                                  | 51  |

|     | Summary                                                                                               |     |

| IV. | SYMBOLIC METHODS FOR REPRESENTATION AND ANALYSIS                                                      | 54  |

|     | Finite State Systems Symbolic Representation                                                          | 56  |

|     | RSchart Symbolic Representation                                                                       | 57  |

|     | Symbolic Representation of "State Configurations"                                                     |     |

|     | Creation of Transition Relation                                                                       |     |

|     | Distributed Statechart.                                                                               |     |

|     | Timed Statechart Symbolic Representation                                                              |     |

|     | Using MTBDDs to Represent Timed Transition Systems                                                    |     |

|     | Creation of Transition Relation                                                                       |     |

|     | MTBDD Image Computation                                                                               |     |

|     | Concurrency in Timed Finite State Representation                                                      |     |

|     | Testing for Set Membership Check for Non-determinism                                                  |     |

|     | Summary                                                                                               |     |

| V.  | SYMBOLIC ANALYSIS OF MULTIPROCESSOR REAL-TIME SYSTEMS                                                 | 87  |

|     | Embedded System Modeling                                                                              |     |

|     | Resource Model                                                                                        |     |

|     | Real-Time Dataflow                                                                                    |     |

|     | Real-Time Dataflow Realization on System Resources                                                    |     |

|     | Kernel Task Execution Policy                                                                          |     |

|     | Kernel Task Communication                                                                             |     |

|     | Generation of Finite-State System Representation                                                      |     |

|     | Generation of Communication Link Finite-State Behavior  Generation of Processor Finite-State Behavior |     |

|     | Generation of Data Source Finite-State Behavior                                                       |     |

|     | System Verification                                                                                   |     |

|     | Reachability Analysis                                                                                 |     |

|     | Schedulability Verification                                                                           |     |

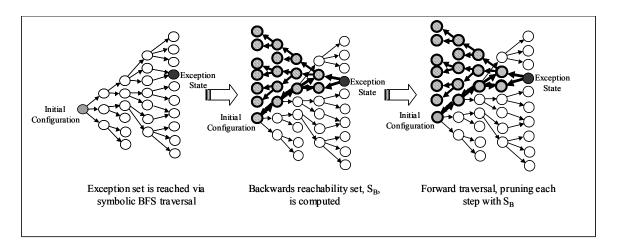

|     | Counterexample Generation                                                                             |     |

|     | Quantitative System Analysis                                                                          |     |

|     | Summary                                                                                               |     |

| VI. | CASE STUDY                                                                                            | 125 |

|     | ATR Algorithm                                                                                         | 125 |

|     | Algorithm Model                                                                                       |     |

|     | System Verification                                                                                   | 129 |

|     | Verification Performance                                                                              | 132 |

|     | Integrated Vehicle Health Management System                                                           | 135 |

|        | IVHM Model                             | 135 |

|--------|----------------------------------------|-----|

|        | System Verification                    | 140 |

|        | Verification Tool Performance          |     |

|        | Comparison to other tools              | 142 |

| VII. R | ESULTS AND FUTURE RESEARCH             | 144 |

|        | Results                                | 144 |

|        | Future Research                        | 145 |

| App    | pendix                                 |     |

| SY     | MBOLIC MANIPULATION ALGORITHMS         | 148 |

|        | Pre-Image Computation (Backwards Step) | 148 |

|        | Zero Unused Output Events              |     |

| AN     | VALYSIS ALGORITHMS                     | 151 |

|        | Throughput Algorithm                   | 151 |

|        | Counterexample Algorithm               | 152 |

| RE.    | FERENCES                               | 154 |

# LIST OF TABLES

| Table |                                                          | Page |

|-------|----------------------------------------------------------|------|

| 1.    | ATR Computation execution times                          | 128  |

| 2.    | TRSchart and corresponding symbolic representation sizes | 133  |

| 3.    | IVHM computation execution times.                        | 139  |

# LIST OF FIGURES

| Figure |                                                                     | Page |

|--------|---------------------------------------------------------------------|------|

| 1.     | VLSI design flow                                                    | 8    |

| 2.     | Coverage vs. Scale                                                  | 13   |

| 3.     | OBDD for $(a \lor b) \land c$                                       | 15   |

| 4.     | OBDDs for $f = (a \land b) \lor (c \land d) \lor (e \land f)$       | 17   |

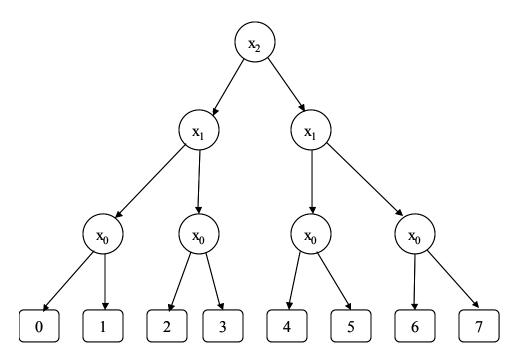

| 5.     | MTBDD mapping 3-bit binary number to its natural number             | 19   |

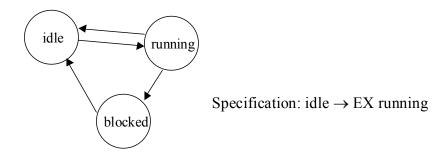

| 6.     | Sample state transition graph with CTL specification to be proven   | 24   |

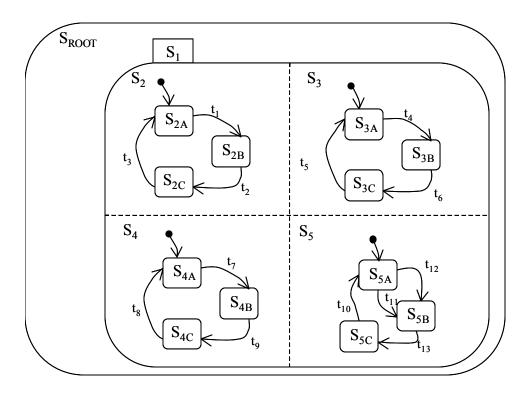

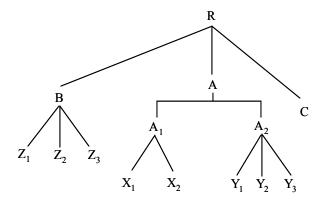

| 7.     | Example statechart                                                  | 38   |

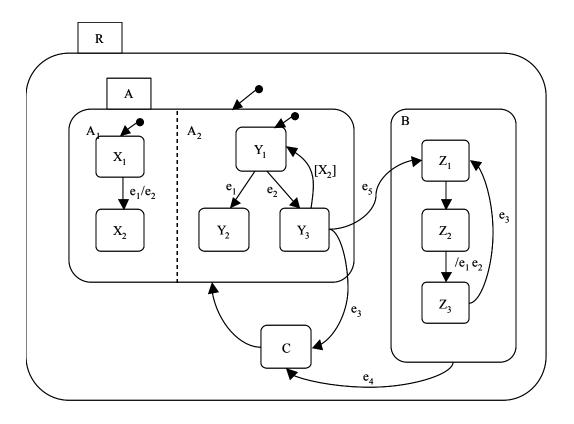

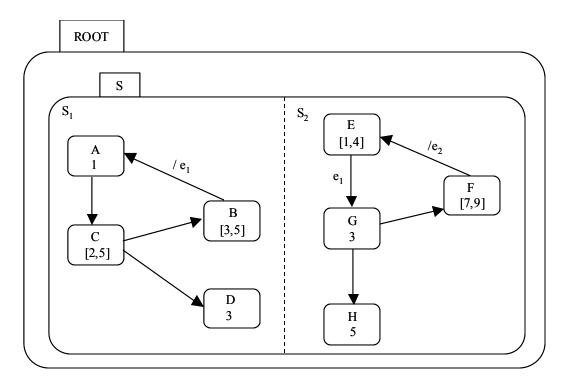

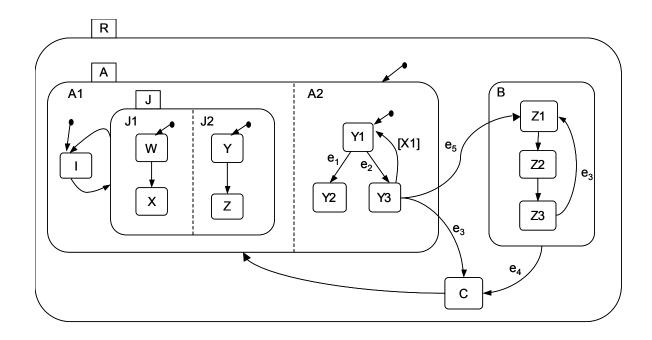

| 8.     | Example RSchart                                                     | 41   |

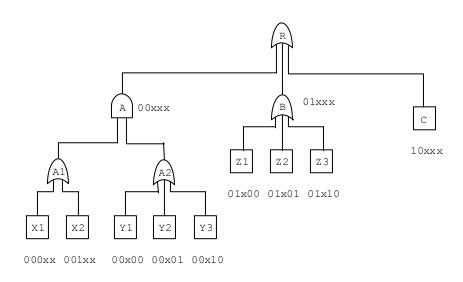

| 9.     | Example RSchart hierarchy structure graph of Figure 8               | 41   |

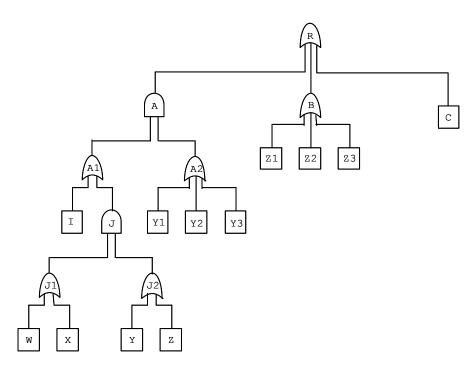

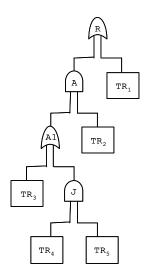

| 10.    | Example TRSchart                                                    | 50   |

| 11.    | Example RSchart                                                     | 60   |

| 12.    | State encodings for the RSchart model in Figure 11                  | 60   |

| 13.    | Sample RSchart                                                      | 67   |

| 14.    | Hierarchy of RSchart in Figure 13.                                  | 67   |

| 15.    | H <sub>MIN</sub> (s) Minimized RSchart hierarchy                    | 68   |

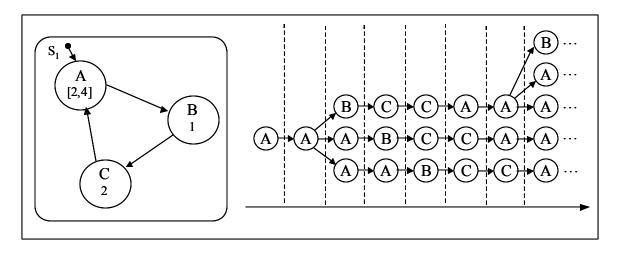

| 16.    | TRSchart and its corresponding behavior trajectories.               | 70   |

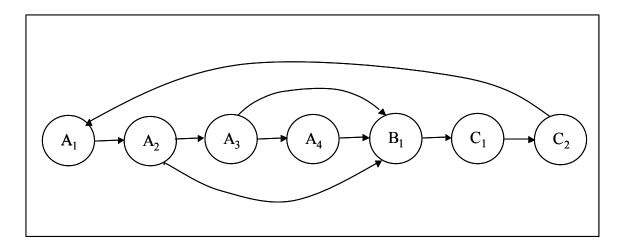

| 17.    | Untimed model equivalent to the TRSchart in Figure 16               | 70   |

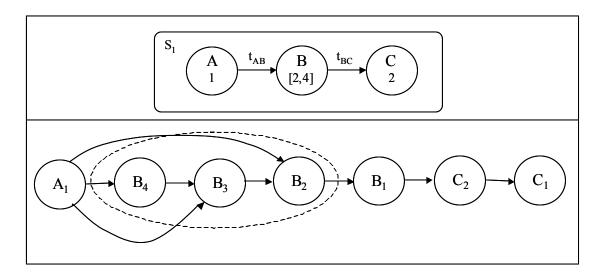

| 18.    | TRSchart with time intervals and associated (finite-state) behavior | 77   |

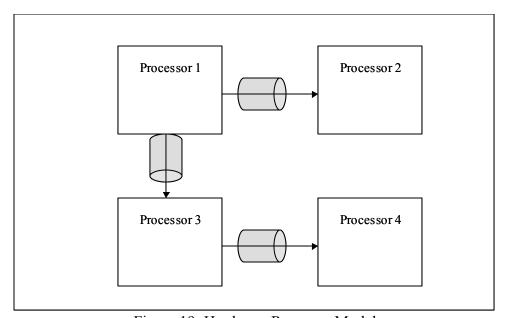

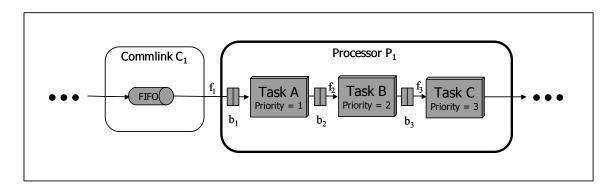

| 19.    | Hardware Resource Model                                             | 90   |

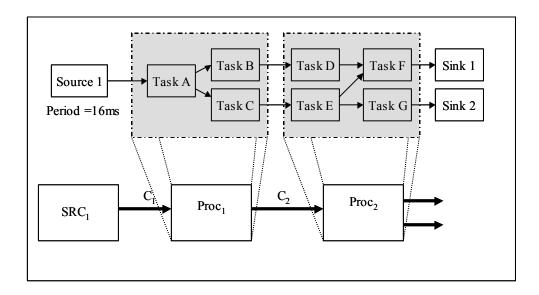

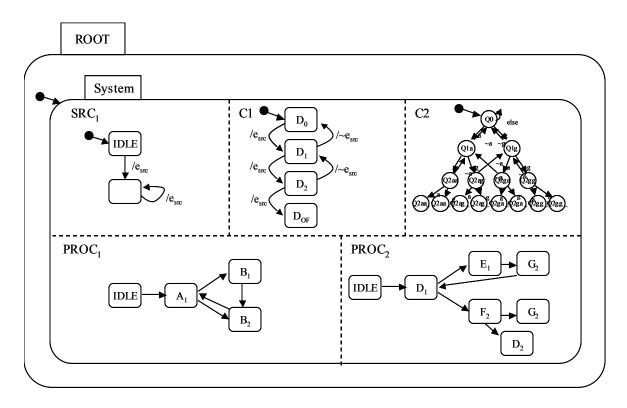

| 20     | RTDF program implemented on two-processor network                   | 100  |

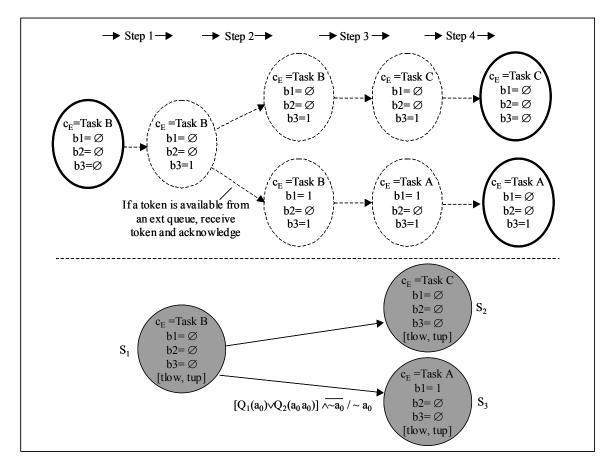

| 21. | TRSchart finite-state behavioral model of system in Figure 20                             | 100 |

|-----|-------------------------------------------------------------------------------------------|-----|

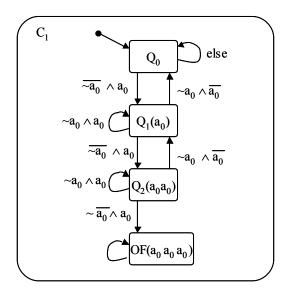

| 22. | Communication channel behavioral model with $L_F=\{a_0\},L_D=2$                           | 103 |

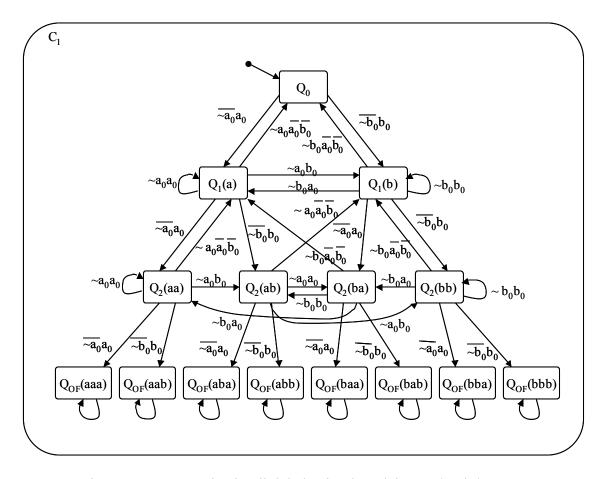

| 23. | Communication link behavioral model, $L_F$ = {a <sub>0</sub> , b <sub>0</sub> }, $L_D$ =2 | 105 |

| 24. | Example RTDF model mapped onto hardware                                                   | 112 |

| 25. | Processor behavior model generation example.                                              | 112 |

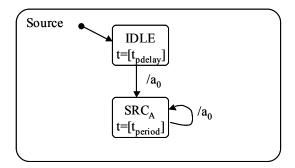

| 26. | Periodic Source Generator                                                                 | 113 |

| 27. | Counterexample construction                                                               | 123 |

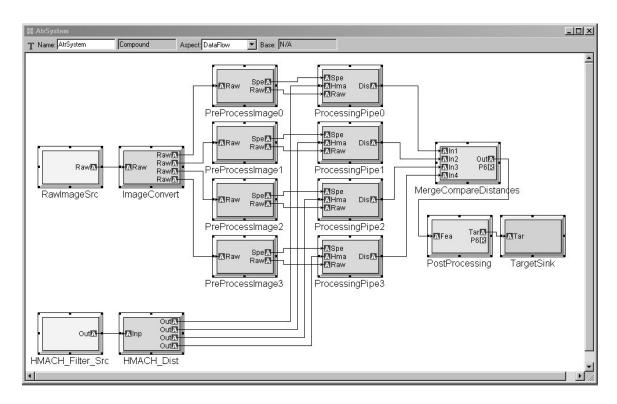

| 28. | ATR RTDF model                                                                            | 127 |

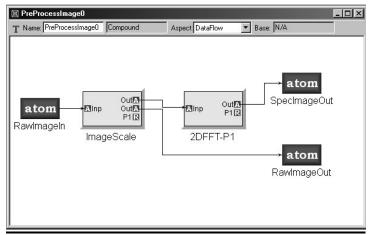

| 29. | PreProcessImage Model                                                                     | 127 |

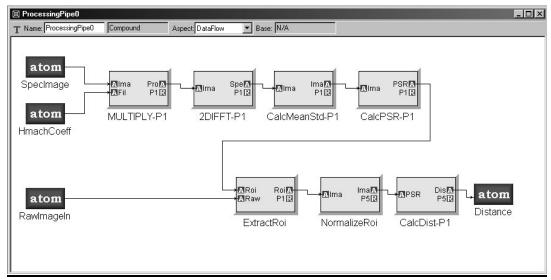

| 30. | ProcessingPipe Model                                                                      | 128 |

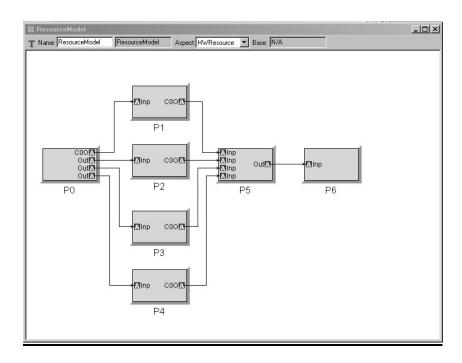

| 31. | ATR Resource Model                                                                        | 129 |

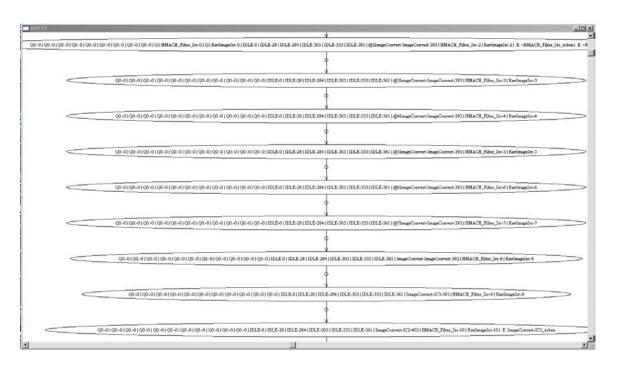

| 32. | Counterexample graphical output                                                           | 130 |

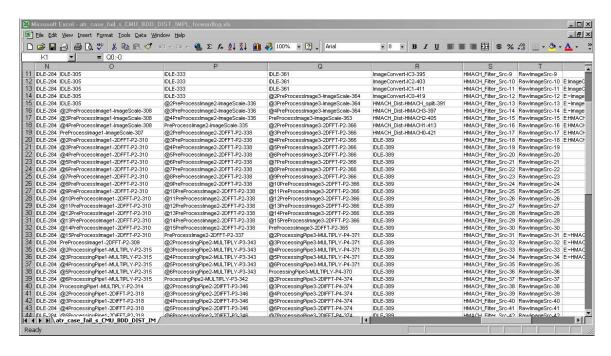

| 33. | Counterexample tabular output                                                             | 131 |

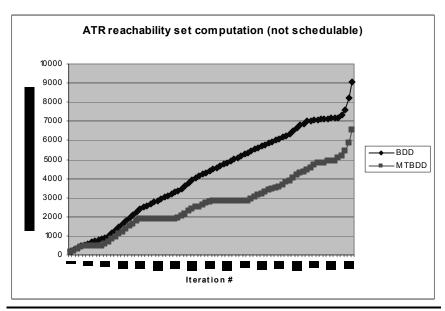

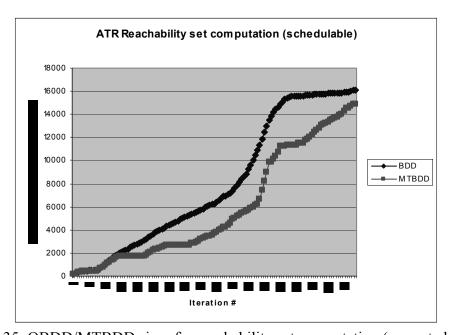

| 34. | OBDD/MTBDD sizes for reachability set computation                                         | 134 |

| 35. | OBDD/MTBDD sizes for reachability set computation (corrected model)                       | 134 |

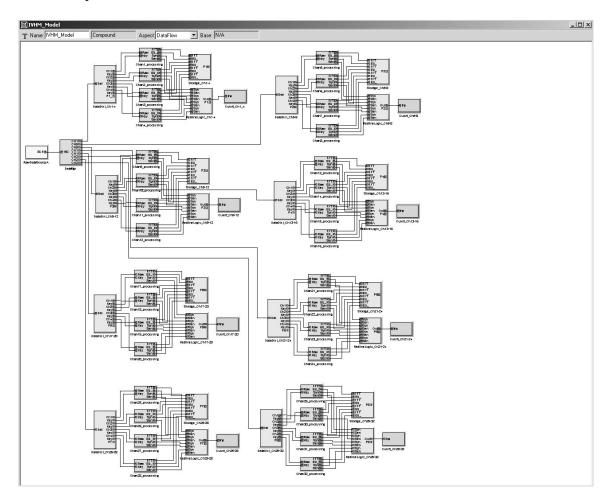

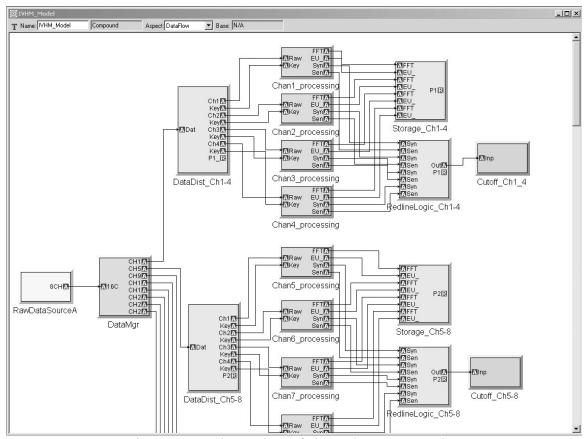

| 36. | IVHM RTDF Model                                                                           | 137 |

| 37. | A closer view of channels 1-4 processing.                                                 | 138 |

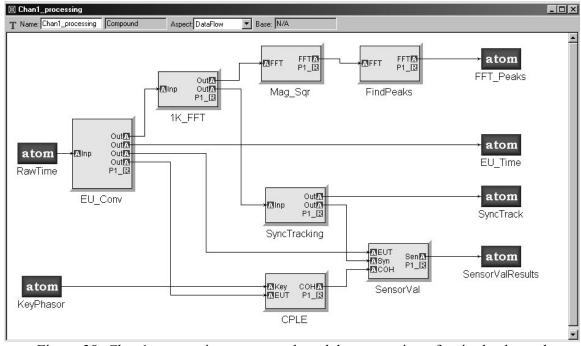

| 38. | Chan1_processing compound model - processing of a single channel                          | 138 |

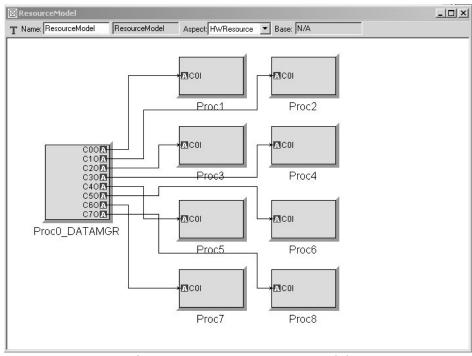

| 39. | IVHM Resource Model                                                                       | 139 |

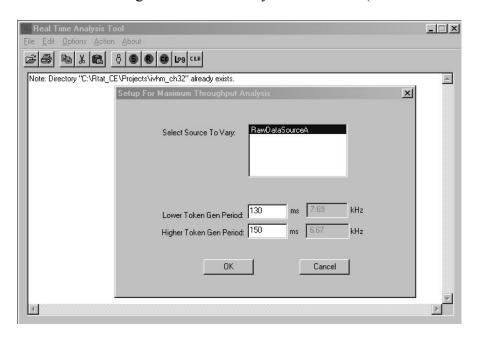

| 40. | Verification tool throughput analysis dialog                                              | 140 |

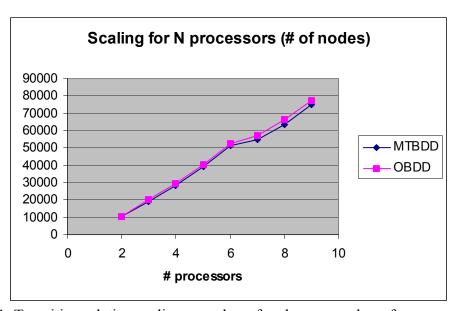

| 41. | Transition relation scaling: number of nodes vs. number of processors                     | 141 |

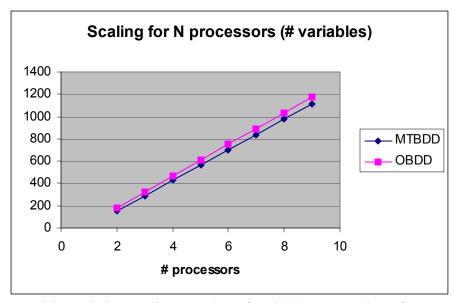

| 42. | Transition relation scaling: number of variables vs. number of processors                 | 142 |

# LIST OF ALGORITHMS

| Algorithm |                                                    | Page |

|-----------|----------------------------------------------------|------|

| 1.        | Implicit transition computation                    | 63   |

| 2.        | Prioritizing transitions                           | 64   |

| 3.        | MTBDD Apply function [16]                          | 74   |

| 4.        | Forward Step Terminal Operation                    | 79   |

| 5.        | Time Tick Terminal Operation                       | 80   |

| 6.        | Set Union Terminal Operation                       | 83   |

| 7.        | Test for Determinism                               | 86   |

| 8.        | Basic Reachability Algorithm                       | 115  |

| 9.        | Reachability Algorithm Using Frontier Set Approach | 116  |

| 10.       | Modified reachability algorithm                    | 118  |

| 11.       | Backwards Reachability                             | 121  |

| 12.       | ZeroDontCareVar algorithm                          | 150  |

#### CHAPTER I

#### INTRODUCTION

Increasingly, especially in the last decade, embedded computer-based systems are used in nearly every aspect of life in the modern world. They typically consist of several processors interacting with each other and interacting with their environment. As of 1999, it has been reported that a fraction of 1% of the world's microprocessors are used in general-purpose computers [3]. The remaining 99% of microprocessors are used in embedded systems. Some of the most important computer systems we depend on today are embedded *real-time* systems. Real-time systems must not only produce correct results but also produce these results in a timely manner. Real-time systems have timing requirements that must be satisfied for the system to operate correctly. In safety-critical applications the consequences of failure of a real-time system to meet its timing constraints can mean disastrous results (financial/property loss, even loss of life).

Real-time embedded system development and implementation are complex tasks. Systems are likely multi-processor systems interacting with several input/output devices and executing hundreds of software tasks. Design automation tools are necessary for automation of tedious and error-prone tasks such as managing the task allocation and communication of such a complex system. Small changes in an application may necessitate many implementation changes that may propagate throughout the entire system. For example, the addition or deletion of a single task may necessitate the reallocation of tasks to other processors in order to load-balance or communication-balance

the system to meet real-time requirements. As embedded systems become more complex due to advances in technology and design automation, verification and analysis tools are a critical part of an overall design approach. It is essential to verify that the system design and generated implementation of that design satisfies system resource and performance constraints.

This dissertation is concerned with system applications in the signal-processing domain. These systems are described with large-grain macro-dataflow models implemented on systems with multiple processing elements (multi-processor systems). Dataflow is well suited for the description of signal processing systems because it is the natural way signal processing engineers specify their algorithms. A dataflow language has several advantages for the programming of multi-processor hardware. Concurrency is explicit in dataflow languages. No additional work is needed to decompose the algorithm into a parallel implementation. Also, the user is insulated from the processor task scheduling that must occur on each processing element. From the user's point of view, the dataflow graph execution must simply satisfy the dataflow semantics.

The dataflow implementation must be verified to be able to execute indefinitely for given input data rates, implying that the necessary size of all buffers must be bounded and, more specifically, fit within available system memory. The system must be proven to be free of deadlock. It must be verified that the system will *always* meet its end-to-end timing constraints. Verification must be performed to determine each of these requirements is satisfied in *all* possible system behaviors.

Although in some embedded system applications, it is possible to statically schedule the system, this is not always the case. Many systems require a dynamic, event-driven scheduler. Also, it is required that tasks not always be simple data transformation

functions. Their behavior may be data dependant. It is not possible to statically schedule components whose behavior is only determined at run-time.

We would, however, like to perform a static analysis / system verification at the time of system generation, accounting for all possible system behavior variations that may occur at run-time. This set of all valid system states is known as the *state space* of the system. The state space of a system may be very large due to the combinatorial growth of the state space for a system with concurrently operating components. This is known as the *state explosion problem*. In this work, non-deterministic behavior is allowed so that behavior that may vary at runtime can be modeled. Non-deterministic behavior causes the number of possible system behaviors (*behavior space*) to grow dramatically, though not necessarily the number of system states.

Even for moderate size systems, the state space can grow to be extremely large. The size can be so large that it is not possible to represent the entire state space explicitly. Note that while it may be possible to represent the state space by creating the concurrent state spaces and maintaining them separately, it may not be possible to examine all possible system behaviors. For complete verification, the ability to traverse the state space examining all behaviors the system may exhibit is essential. Verification through simulation is not an option for such a large number of possible behaviors the system may exhibit due to non-deterministic behavior present in the model. A formal method known as symbolic model checking has had success in providing exhaustive verification of extremely large state spaces [4].

Model checking is a verification technique providing exhaustive examination of a system through the exhaustive exploration of a state space. Symbolic model checking provides exhaustive verification of a system by implicitly representing a state space

through the use of a symbolic representation. It is called symbolic because it is based on the manipulation of Boolean formulas [1].

Frequently, symbolic model checking takes the form of a method for representing a finite-state transition system with the graph-based Boolean function representation ordered binary decision diagrams (OBDDs). OBDDs have been proven to work well in many cases for the representation of extremely large state spaces. OBDDs have had their greatest success in commercial hardware VLSI verification tools where very large designs must be managed efficiently [5]. Symbolic model checking uses a formal methods approach to system verification with the advantage that the users needs no special expertise in mathematical disciplines as is the case with using formal methods based on theorem proving.

The research presented in this dissertation focuses on the development of an analysis and verification system employing OBDD and a variation of OBDDs, known as MTBDD (Multi-Terminal Binary Decision Diagrams), based symbolic model checking techniques. The techniques resulting from this research will be used to verify schedulability, deadlock-free operation, and real-time timing constraints. The following statement represents the main objective of this research:

The goal of this research is to develop an efficient analysis and verification system for multi-processor, real-time systems using symbolic techniques.

A verification tool, Real-Time Analysis Tool (RTAT), has been developed implementing the model checking strategies for real-time systems presented in this dissertation.

The system model is a dataflow graph implemented on multiprocessor hardware.

This model can be used for system synthesis. The verification tool operates on this same

system model and can provide verification of both design and implementation correctness. In contrast, other widely used model checking tools require the user to provide a behavior model of system operation, usually created by hand from a system design description. If implementation verification is desired, the user must create a behavioral model of the system, usually abstracted by hand from a system implementation.

In this work, verification questions are posed in terms of *system* correctness. The use of other verification tools requires that the properties to be verified must be specified in terms of the underlying behavioral model of the system. These properties are usually specified in terms of a temporal logic, such as computational tree logic (CTL), that can be difficult for the user to express system level properties.

#### The main contributions of this dissertation are:

- An approach for the efficient modeling and analysis of *timed* finite-state systems is presented. Methods to analyze these models based on model checking techniques are developed using OBDDs and MTBDDs as the underlying representation of a finite-state behavior graph.

- A method for *exhaustive* verification of multi-processor real-time systems using a timed finite-state model-checking approach is presented. This dissertation tackles the problem of *schedulability* verification of a design and its implementation. Schedulability is defined as follows: "If a system is able to execute its dataflow graph continuously in all possible cases, then the system is schedulable." Also, *performance analysis* using the same underlying model checking approach is

presented which is capable of finding performance extremes, e.g., maximum throughput, is also explored.

## Overview

Chapter II gives background information on formal verification, the symbolic representations of OBDDs and MTBDDs. Also given is background information on relevant model checking tools and current approaches to real-time system design focusing on scheduling approaches. Chapter III presents the general models of computation used in this work along with the variations tailored for use in this dissertation work. Symbolic methods utilized for the foundation of exhaustive system behavior analysis are detailed in Chapter IV. Chapter V presents a system verification method using a symbolic representation as the underlying computation engine. Chapter VI presents a case study and demonstrates the performance of the analysis methods presented in this work and their usefulness in the verification of a practical application. Chapter VII concludes with results of the research and future directions.

#### **CHAPTER II**

#### BACKGROUND AND RELATED APPROACHES

This chapter provides a description of the general approaches to formal system verification. The dominant approaches, theorem proving and model checking, are described along with an efficient approach to model checking and symbolic model checking. The next section describes the symbolic representations used in symbolic model checking. Ordered binary decision diagrams (OBDDs) are a symbolic representation that has had much success in verification of large hardware verification problems and has been incorporated as the internal representation of many commercial VLSI CAD tools in the last few years. Also presented are Multi-Terminal Binary Decision Diagrams (MTBDDs), a variation of OBDDs utilized in this dissertation, and a brief overview of other OBDD variants and a few of the popular OBDD implementations. Several research-quality model checking tools are available for both reactive and reactive real-time systems. A description of selected model-checking based verification tools is presented.

#### Formal Verification

Due to the rate at which integrated circuit size and density is increasing, the size of the systems being designed is also increasing at the same rapid pace. Verification technology must keep pace with systems being verified. In the past hardware designs were simply verified using ad-hoc methods: testing of the actual system or using simulation engines, exciting the circuit with all possible input combinations (or as many

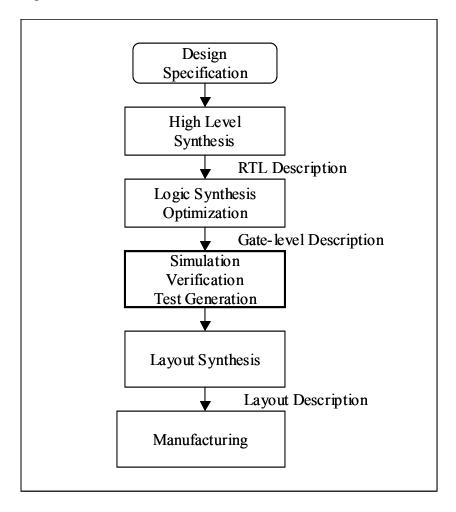

as were feasible to try within time/cost constraints). Figure 1 shows a VLSI design flow. Currently extensive simulation via hardware CAD tools is the predominant technique used to test and verify hardware designs. Extensive verification is performed after the Logic Synthesis and Optimization stage, although simulation can be performed at multiple levels in the design process. Early in the design process, the abstract register transfer language (RTL) [2] level design can be simulated and checked for errors. As the design progresses to the gate level and finally the transistor level, simulation must continue to try to find errors that may have occurred during the implementation and refinement stages.

Figure 1: VLSI design flow

As designs are now well into the millions of transistors and with this number increasing rapidly, total coverage of the circuit behavior through simulation becomes a problem growing faster than the design problem itself. Exhaustive simulation is not feasible. The design may be broken into sub-systems for a more manageable size, but the interaction of these individual parts must be verified to operate correctly. When simulating circuits with a large number of possible states the probability of missing an error becomes more likely.

Software designs, high-level protocol descriptions, and real-time systems have typically had even less rigorous methods of testing. For verification of large-scale, system-level problems, more automated, efficient methods of verification are needed. Formal verification is attractive because it offers *complete* coverage of the entire operation of the system. In other words, formal verification is as good as exhaustive simulation.

Many different types of system design problems have been tackled using formal verification techniques:

- Circuit verification RTL level, gate level, transistor level [6]

- Protocol verification Communication protocols such as PCI, SCI [7]

- High-level system verification Interactions between physical hardware,

solid-state electronics, microprocessor operation [1]

There are two main types of formal verification being used today: theorem proving and model checking.

# **Theorem Proving**

One type of formal verification is *theorem proving*. In theorem proving the system model and the system specifications to be proven are described in terms of mathematical statements. Verification proceeds by proving theorems about the system. The proof must show that the statement of the theorem can be formally derived from axioms using inference rules. Theorems must be developed and proven true in order to verify the system model satisfies the specifications.

Automatic theorem provers are available to assist in the mechanical details of this process but, in general, these are semi-automatic at best and have not made it into mainstream tools. The users must be experts of logic to perform the tedious task of writing the axioms to be proven [8]. The user must guide the verification process. Because of the level of knowledge required and the manual nature of theorem proving, this method of verification is an expensive process in terms of the time and training required.

# Model Checking

Temporal logic model checking was first developed by Emerson and Clarke in 1981 [9]. In this approach, a finite-state transition *model* of the system is created that represents all possible behaviors. Then model is *checked* for satisfaction of a specification by exploring all possible behaviors with a model checking "engine".

Specifications of the system to be verified are supplied in the form of a temporal logic. Model checkers exhaustively explore the state space of the state-transition system model to verify that the model satisfies the specification. Model checking provides coverage of the *complete* behavior of the system, not just behavior excited by a set of

simulation vectors. An important point is that this procedure requires *no* user intervention, unlike theorem proving – the proving of the specification is completely automatic. If the model checker finds that the specification is not satisfied, most model checkers have the ability to return a counterexample. This counterexample is a state sequence that violates the specification.

The early model checkers used exhaustive analysis techniques and were limited to fairly small models by today's standards. The number of states that must be explicitly represented and checked using this method may grow exponentially in proportion to the number of sub-systems acting concurrently in the model [4]. When the models become too large for conventional model checkers to handle, model abstraction and state space reduction methods can be used to reduce the state space to a manageable size at the cost of some loss of information. This may be unacceptable for the verification of safety critical systems, for example. A fairly recent approach that has been developed in the last ten years is a *symbolic* method of model checking. Because this new form of model checking can allow a larger state space to be explored, the need to use reduction methods is lessened.

# Symbolic Model Checking

The limiting factor of model checking is the representation of the extremely large state spaces that can occur. When the system has components operating concurrently that may transition in parallel, the state space grows as the product of these concurrent state spaces. Since the introduction of model checking, advances have been made to make the representation and manipulation of these large state spaces feasible. In 1987, McMillan realized that the state-transition model could be much more efficiently manipulated if

represented implicitly with *ordered binary decision diagrams* (OBDDs) [9]. OBDDs were introduced in their current form by Bryant in 1986 [10]. This new form of analysis that operates directly on the model represented by symbolic equations rather than explicit enumeration of states is known as *symbolic model checking*. Although still limited by the state explosion problem, the OBDDs go a long way to mitigate the problem.

Symbolic model checking has proven to be successful because of the use of OBDDs to provide an efficient representation of the state space. The biggest gains of using a symbolic method are realized when analysis algorithms can operate completely within this symbolic domain. For example, reachability analysis can be performed to find the set of states that are reachable from a given initial state set. This algorithm operates only on state *sets* rather than individual states, providing a much more efficient method than a standard traversal of the state space that must examine individual paths.

Symbolic methods also work well when examining the behavior of non-deterministic systems. A traditional simulator examines a single state sequence path. Symbolically we can, through the use of state sets, examine all paths simultaneously. This is essential for the exhaustive analysis of large systems - systems too large to verify through the use of exhaustive simulation. A verifier must examine *all* possibilities.

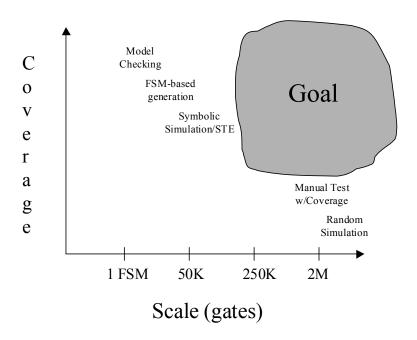

Although oriented towards the verification of hardware circuits, the graph shown in Figure 2 gives an idea of the current state of design verification tools and the relative amounts of design coverage provided for given design sizes. On one end of the spectrum, model checking provides complete coverage but with a limit to the size of the systems it can cover. Simulation can operate on the largest of designs but has a very limited amount of design space it can cover.

The practical use of symbolic model checking is limited by the state explosion problem as was non-symbolic model checking but now the sheer number of reachable states is not necessarily the limiting factor in system verification. The size of the OBDD that represents the system is now the bottleneck. One goal of this work is to improve on the use of the OBDDs for the symbolic representation of complex systems modeled at a higher level of abstraction such as modeling the interactions system components, as opposed to the modeling of a hardware circuit. The more efficiently the model can be represented symbolically, the larger the models that can be analyzed.

A much more difficult problem is the verification of timed systems. These systems can exhibit exponential growth with respect to the number of clocks. An efficient method is also needed to represent these systems symbolically.

Figure 2: Coverage vs. Scale

# Symbolic Representations

Ordered Binary Decision Diagrams are widely used with success in several areas including verification of VLSI designs and symbolic model checking. Also presented in this section are variants of OBDDs, one of which is the Multi-Terminal BDD (MTBDD) that is also used in this work.

# Ordered Binary Decision Diagrams

Ordered binary decision diagrams, as proposed by Bryant, are a canonical structure used for representing Boolean functions [10]. The OBDD structure is usually a more compact representation than traditional sum-of-product/product-of-sums representations especially for large functions. Operations can be performed on OBDDs in a very efficient manner. These properties have in recent years made OBDDs popular for use in a variety of systems where very large state spaces must be managed efficiently.

OBDDs take the form of a directed acyclic graph. Each internal node of an OBDD is labeled with a variable of the function the OBDD is representing. For each internal node there are two edges leaving that node labeled 1 and 0. Every OBDD has exactly two leaf nodes that represent the values *true* and *false*. The graph structure described forms a type of decision tree where all variable assignments that satisfy the represented function *f* lead to the *true* leaf node and all other assignments lead to the *false* node. The OBDD structure has a single root node. As the name implies the variables have a strict fixed ordering. A consequence of this is, as a path is traversed from root to a leaf, or terminal node, each variable node is encountered only once. OBDDs are a reduced, canonical structure also referred to as ROBDDs or BDDs. Due to their canonical property, OBDDs representing the same function are isomorphic. This

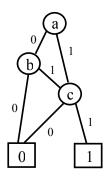

property allows efficient equivalence checking. Figure 3 illustrates the OBDD for the Boolean formula  $(a \lor b) \land c$ .

Figure 3: OBDD for  $(a \lor b) \land c$

Basic OBDD functions include the standard Boolean operators: equivalence, AND, OR, NOT, etc. These algorithms have time and space complexities that are polynomial with respect to the number of OBDD nodes of the operands. This means that for reasonable sized OBDDs the worst-case performance of an operation remains reasonable [11]. OBDDs do have their drawbacks. There are some functions for which OBDDs simply cannot provide an efficient representation, such as a multiplier. An OBDD representation of a multiplier requires a number of graph nodes that grow exponentially with respect to the input word size [10]. With that said, OBDDs do perform well for the representation of many practical applications.

#### *Variable ordering*

The ordering of the variables (the ordering of the levels within the graph) can have a dramatic effect on the size of the OBDD. A bad variable ordering can greatly

increase size and time required to perform operations on that OBDD and, sometimes more importantly, the OBDD may be too large to fit in the computer's physical memory. Using virtual memory is usually not an acceptable solution since memory accesses to OBDD structures are very irregular and causes a large amount of page faults.

For some choices of variable ordering the representation of a function can grow exponentially as the number of variables grow, while for other choices of ordering may only be of linear growth [12]. By using common sense in choosing the variable ordering or using a heuristic developed for the particular application, these problems can usually be avoided.

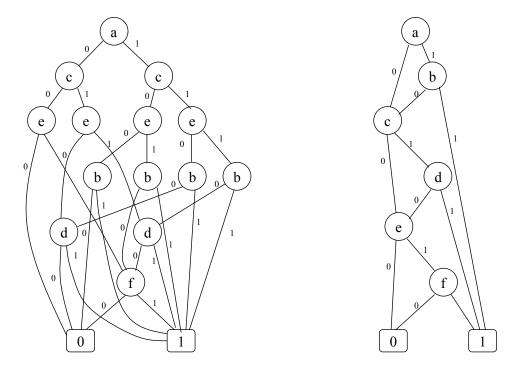

The example in figure 3 shows two OBDDs with different variable orderings representing the same function ( $f = (a \land b) \lor (c \land d) \lor (e \land f)$ ). The OBDD on the right has a well-chosen variable ordering. In this case the variable ordering is optimal for this function. Only 6 nodes are needed. The OBDD on the left has a variable ordering that produces an OBDD that requires 14 nodes to represent the same function.

Ordering: a < c < e < b < d < f

Ordering: a < b < c < d < e < f

Figure 4: OBDDs for  $f = (a \land b) \lor (c \land d) \lor (e \land f)$

Some applications using a static variable ordering throughout application may not produce acceptable results. In this case *dynamic variable ordering* may be needed to maintain manageable OBDDs. Dynamic variable reordering is a method for automatically changing the variable ordering to find an improvement in the size of the OBDDs. Many OBDD packages have support for dynamic variable ordering [18][19].

Many heuristics for dynamic variable ordering have been proposed. These heuristics can be divided into two categories: reordering on a global level and reordering on a local level. A common local reordering method is known as *sifting*. Sifting is a method to swap adjacent variables to search for a better variable ordering (fewer OBDD nodes). Reordering on a global level proposes a completely new variable ordering. This global rebuilding is much more time consuming but also has greater potential gains.

Dynamic variable reordering is an attractive option because it is fully automatic. The only drawback is the large amount of time it takes to search for a better variable ordering. Using this strategy can sometimes be the difference between completing an operation or it ending in failure because system memory has been exhausted, although a performance penalty is paid. It can slow down the application by as much as a factor of 10 [13].

#### **MTBDDs**

Many extensions to the basic OBDD form have been proposed. One of these extensions is the multi-terminal BDD (MTBDD). The MTBDD represents *pseudo* Boolean functions [14]. MTBDDs map bit vectors of Boolean values (which may represent a set) to a finite set of elements (integers) instead of only to the values true and false as in standard OBDDs.

More formally, MTBDDs are used for representing functions of the form  $f: B^n \to N$ , where f is a function that maps Boolean vectors of length n to integer values [15]. The function f effectively partitions the space of Boolean vectors,  $B^n$ , into M sets, where M is the number of integers the sets are being mapped onto. A similar representation to MTBDDs would be to use an array of OBDDs, with each OBDD representing a set that can be associated with a corresponding integer value.

MTBDDs range is Boolean, but their domain is arbitrary, defined to be the set of integers, N. Figure 5 below shows an MTBDD function,  $f=4x_2+2x_1+x_0$  which maps 3-bit binary numbers into the corresponding natural number [16].

Figure 5: MTBDD mapping 3-bit binary number to its natural number

The reduction rules are the same for MTBDDs as they are for OBDDs and MTBDDs exhibit the same canonical property as OBDDs. However, since the image/result of function represented by MTBDDs is a member of N, Boolean operations are no longer applicable [17]. With that said, the mechanics of operations applied on MTBDDs work in much the same way as OBDDs. The *apply* routines traverse the MTBDDs beginning at the root applying a Boolean operation on the way down the structure. When terminal nodes are reached the terminal transformation is applied. This transformation takes two terminal nodes and produces a new one. In this way, same as OBDDs, new graphs are built up from the recursive application of a transformation function.

# **OBDD** implementations

The efficiency of the techniques used to implement the OBDDs and the operations on them are critical to their performance. During the course of any OBDD operation many OBDD nodes are created and destroyed. For operations on large OBDDs hundreds of thousands of nodes may be created and destroyed in the intermediate steps of a single operation. Efficient memory management is crucial. Since all nodes are of the same size, structure overhead can be reduced by using a garbage collection strategy. In one such strategy, deleted nodes are not immediately *free*'ed but are put in a free list to be reused if possible so that expensive operating system *free/malloc* calls can be avoided.

Most OBDD packages have a type of operation cache where computed functions are stored. This cache stores the operation performed and its corresponding resultant OBDD. *Strong canonicity* should be always guaranteed by the OBDD implementation. Strong canonicity defines that in an OBDD implementation if f and g are equivalent functions, then not only are their representations the same, but they are, in fact, represented by the same structure in memory [16]. The pointer that points to the OBDD of f and g will point to the same structure. As a result of this property, to perform a test to determine if two OBDDs are equal, the user must only compare their pointers to determine equivalence. If they are equivalent then they must point to the same structure [5].

There are several OBDD packages that exist, each with different features. Some features that separate the implementations are efficiency of the package, the methods of dynamic variable ordering that the package provides, and support for other OBDD variations that may be needed. The most notable OBDD packages are:

- <u>bddlib</u>: <u>bddlib</u> was developed by David Long at CMU. This implementation has been widely distributed both stand alone and as a part of SIS system discussed later [18]. This package has support for dynamic variable ordering through the use of sifting and window permutations. <u>bddlib</u> has some limited support for MTBDDs.

- CUDD: CUDD was developed at the University of Colorado at Boulder by Fabio Somenzi. CUDD has support for dynamic variable ordering using random variable exchange, sifting, group shifting, window permutations, simulated annealing, genetic algorithm-based reordering, and identification and linking of symmetric variables. CUDD supports OBDDs, ADDs/MTBDDs, and ZBDDs. This package shows a good tradeoff between memory usage and execution time [20].

Both *bddlib* and *CUDD* packages are used in this dissertation work. *bddlib* is used for OBDD implement and *CUDD* is used to MTBDDs implementation.

# Model Checking Tools

#### **SMV**

The SMV (Symbolic Model Verifier) system is a tool developed by McMillan at Carnegie Mellon University for checking modeled finite state systems against a specification described using a temporal logic (Computational Tree Logic, CTL) [9]. SMV was designed to be an experimental tool for exploring the practicality of model checking and how it applies to hardware verification. SMV has become somewhat of a point of reference in the model checking research community. Many researchers

exploring state-space representation and traversal optimization techniques have used SMV as the platform for implementing their own algorithms and extensions [21].

The SMV language is used to describe a finite transition relation model. This relational model is represented symbolically as an OBDD. Properties of the model to be verified are specified in a temporal logic, CTL. Efficient OBDD-based algorithms are used to verify that the model satisfies the CTL specifications. If the model checker finds that a specification can be violated, a counterexample may be generated which demonstrates a sequence of events in the model that leads to a fault.

The language provides for the descriptions of reusable *modules* and hierarchical definitions. Synchronous and asynchronous models may be described. In a synchronous composition of modules, when a single step of this composition is taken, a single step is taken in each of the modules. In an asynchronous, or *interleaving*, composition of modules, when a step of the composition is taken, a step is taken by exactly one component [1]. The SMV language also provides for the description of non-deterministic behavior. Although the SMV language supports arithmetic integer operations, it has a very inefficient implementation. SMV also does not support a true timed model. If timing is to be represented, the underlying model will be a series of states with each state representing the passage of one unit of time. It is easy to see how this method is not feasible for systems with large delay times.

NuSMV is a reimplemented and reengineered of the original SMV model checker, introduced in [22]. NuSMV supports a user interface with an interactive shell. To support larger state spaces, NuSMV implements both the conjunctive and disjunctive partitioning methods of [23]. The modeling language remains the same along with the temporal logic specification language, CTL. Support for model checking of LTL

specifications was added via a reduction of LTL specifications to CTL. Also, the underlying OBDD implementation was changed to use the CUDD package [19]. The current release is NuSMV 2, which adds model checking techniques based on prepositional satisfiability techniques (SAT) [24].

Computation Tree Logic, or CTL, is a propositional, temporal logic used in SMV to express properties of a model to be verified. The CTL specifications operate on a *computation tree* model of the system. A computation tree is a structure derived from a finite state graph by unwinding the state trajectories and producing a tree structure [25]. The computation tree represents essentially the traversal of a finite state graph beginning at a declared root state. The root may be any state; it is the point at which the CTL property is referenced. A CTL formula describes properties of the paths leaving the root state. CTL is classified as a *branching time* logic since it can describe properties of multiple paths leaving the reference state.

CTL formulas are composed of atomic propositions, Boolean connectives, and temporal operators. The Boolean connectives are  $\neg$  (not),  $\land$  (and), and  $\lor$  (or). The temporal operator is composed of a path quantifier and a linear time operator.

The linear time operators used to express temporal relations are as follows:

- X f state f is immediate successor

- G f state f holds for all states on path

- F f state f exists in the future

- $f \cup g$  from state f until state g

The linear time operators describe behavior along a single path. The path quantifiers are branching time operators meaning they operate on a branching tree structure. There are two path quantifiers, A and E. The universal path quantifier A

represents that *all* paths are referenced from the root state. The existential path quantifier *E* represents that the property references *some* path from the root state. The possible CTL operators are enumerated as: EX, EG, EF, EU, AX, AG, AF, and AU.

Figure 6: Sample state transition graph with CTL specification to be proven

A simple example of computing CTL constraints is the verification of the formula  $S_0 \rightarrow EX$  a. From Figure 6 we can choose a to be state *running* and  $S_0$  to be state *idle*. The CTL formula EX a must be computed. EX a represents the set of all states that may lead to the state set a in a single step. From the system model EX a is the state set that results from a single backwards step from state a. For the example above, EX *running* is equal to the state set {*idle*}. In this case the specification  $idle \rightarrow EX$  *running* is satisfied since  $S_0$  is contained in the resulting state set.

The combination of these two types of operators allows for the description of many temporal properties of systems that can be checked such as safety properties and freedom from deadlock. For example, specifications such as: *the brake caliper will always activate (sometime) after the break pedal is pressed* (AG (pedal\_press->AF activate)), or *the brake caliper will always activate the next time (next system state) after the break pedal is pressed* (AG (pedal press->AX activate)). CTL cannot express quantitative

temporal properties such as: the brake caliper will always activate within 1 second of a brake pedal press.

Efficient algorithms exist for verifying that the system model satisfies the CTL specification [16]. These algorithms use the symbolic model of the system that is in the form of a Boolean next-state transition relation. This equation is, in turn, represented in the form of an OBDD. Using the OBDD representation of the system model there is no need to explicitly build the computational tree structure to verify the CTL specifications. A CTL formula can be identified by a set of states (represented with an OBDD) derived from the model that satisfies the formula. The model checking of the CTL formula only requires traversal of the model and manipulation of sets of states. For example, to compute EXa a single backwards step (sometimes called pre-image) is computed. Using the OBDD representation to verify the specifications provides an efficient method of model checking.

Although CTL specifications are able to assert many of the desired properties of systems, it cannot describe important quantitative information that is essential in verification of real-time systems (of course, this also assumes an underlying timed model structure would be needed). To address this problem several other variants of CTL have been proposed that include quantitative timing information to describe specifications for these types of systems. SMV does not support any of the timed variations of CTL.

#### Verus

Verus is a system used for the specification and verification of real-time systems. The goal is to provide insight into *how well* a system works rather than just determining *if* it works by way of computing its timing characteristics [25]. The Verus language is used

This specification of the system is then translated into a state-transition graph. Model checking algorithms are used to verify the specified properties and extract performance data about the system. Schedulability of processes can be verified by finding maximum times between processes execution. Verus has the capability to give a counterexample sequence of states when a property is not satisfied. The Verus system can also be useful with untimed models as well. Campos claims models with up to  $10^{30}$  states can be verified in minutes with this system [27].

The Verus language is a simple language that looks similar to C. Variables may be local or global (to a process). Concurrent processes may be modeled with interaction possible through global variables. Variables are also identified as internal or external. External variables are set from sources outside the system that are not influenced by the model. The value of external variables can change non-deterministically at any transition of the model. Variables may be defined as one of two data types: integer and Boolean.

Several primitives specific to temporal model definition are available:

wait - The wait operator is available to represent the passage of time. All other operations are defined to occur in zero time. The state of a process can only be observed when a wait condition occurs.

select - The select operator is used to explicitly define non-deterministic action in the program flow.

*periodic* - The periodic statement is used to declare a section of code enclosed in brackets as executing periodically. This statement has several parameters:

start\_time - the time that will pass before the code begins execution for the first

time

period - the period at which the code will execute

deadline - if the code does not finish in this length of time an exception will be raised

Deadlines may also be specified in aperiodic processes using the *deadline* statement which declares that a segment of code enclosed in brackets must finish execution within the amount of time specified in the deadline statement. When a deadline, either defined by the periodic or deadline statement, is missed, an exception handler is executed. The exception handler is a segment of code within brackets designated by the keyword *handler*. After the handler code is executed, the rest of the code in the deadline scope is ignored and control resumes at the next statement after the deadline code.

Verus has some command-line options that can enable features to increase performance. Normally, Verus uses a single monolithic transition relation to represent a system that may be a composition of the individual transition relations of concurrent processes. Computing the composition of the smaller transition relations (in terms of OBDDs) can cause a state explosion. An option is available to keep these individual

transition relations separate. This option generally uses less memory and may be necessary for some systems. It does complicate the computation of a basic step since multiple relations must be dealt with.

Verus also has support for automatic variable reordering of the model before the global transition relation of the system is constructed. This reordering process permutes variables to produce a smaller OBDD representation. Since this can be a very lengthy process, support is provided to save a specific variable ordering to a text file that may later be reloaded instead of performing the reordering process again. Campos states that it is beneficial to experiment with the variable ordering as the model is being built. Since the automatic variable reordering moves single variables to produce incremental improvements, better results can be obtained using this method on small sections of the model rather than simply beginning with the final large model.

Manual reordering may be also used to find a more compact OBDD. Common sense approaches such as placing variables that make global decisions about the system should be placed first in the ordering. Variables that are closely related should be placed together (such as present state and next state variables). These are only general recommendations and may not apply to all types of systems.

The current released version of Verus is 0.9. Some of the special primitives of the language have not yet been implemented. This version only supports unit-time wait statements (wait(1)). To create a state that lasts 5 units of time 5 wait statements must be used. This makes the tool unsuitable for use on any system with large or widely varying times on transitions that cannot be reduced by a common factor manually at the modeling level. This tool simply expands the timed finite state model into a standard finite state model. The state transition times are presumably expanded to strings of unit length

states. A state transition that is labeled 5 units of time is translated to a FSM form of a string of 5 standard states. This causes the internal representations of timed systems to grow at an exponential rate with respect to the number of states modeled. This current version does not produce counterexamples, but it will produce a restricted form of a counterexample by placing the EXAMPLE attribute on a CTL specification.

### **UPPAAL**

UPPAAL is a set of tools for system validation and verification of real-time systems [28]. The UPPAAL system consists of a description language, simulator, and a model-checker. Systems that are suitable for verification with this tool include systems that can be represented with a collection of timed automata. These timed automata can represent non-deterministic processes with real-valued clocks. These processes interact through defined communication channels or shared variables.

UPPAAL allows entry of the timed automata description language in both graphical and textual formats (the graphical format is translated into the textual format). The simulation engine allows the user to interactively (graphically) examine the behavior of the model. Using the simulator, only a single execution trace can be followed. The simulator is provided as a means of debugging the model itself (or debugging of the system design if it is the beginning of a design process). The simulator also allows the user to graphically explore an execution trace that is produced from the model checker.

Extensions have been made to the UPPAAL description language to extend the timed automata with the use of data variables (real-valued integers and Boolean variables) to make the description language more like a high-level programming

language. The possible values the variables may represent must be bounded or verification may not terminate.

UPPAAL attacks the state explosion problem through the use of symbolic modeling techniques and compositional techniques. The system is modeled as a parallel composition of automata in the form:

$$\mathbf{A} = (\mathbf{A}_1 | \mathbf{A}_2 | ... \mathbf{A}_n)$$

The state space is explored in terms of symbolic states in the form of (l, D) where l is a control node vector of length n [28]. An element of l,  $l_i$  corresponds to a state in  $A_i$  specifying the current state of each of the timed automata and D is a set of clock constraints. A symbolic state (l, D) represents a set of all the states (l, u) where the clock variables u satisfies the constraint D [29]. In this representation the data and shared variables are treated in much the same way as clock variables. A model-checking procedure is used in UPPAAL to determine whether or not the timed automaton A satisfies a given formula  $\varphi$ . The property  $\varphi$  must be of the form:

$$\varphi := \forall \Box \beta \, | \, \exists \Diamond \beta \qquad \beta := \alpha \, | \, \beta 1 \land \beta 2 \, | \, \neg \beta,$$

where  $\alpha$  is an atomic expression that may be a clock constraint or a state constraint.  $\forall \Box \beta$  denotes the expression  $\beta$  must be satisfied for all reachable states (from a given initial state set).  $\exists \Diamond \beta$  expresses  $\beta$  must be satisfied for some reachable state set [30].

From an algorithm point of view the model checking of the specification proceeds much as it does for other finite-state model checking reachability analysis algorithms. The state space is explored in a breadth-first manner until the real-time property is proven true or false. For the examination of the state space, UPPAAL also uses an "on the fly" verification method. The full state space of the automaton is never explicitly produced.

This method requires more overhead on each iteration but avoids the enumeration of the entire state space. If the verification is limited to a single automaton, then only that part of the model will be examined. Using the on-the-fly traversal method if similar properties are to be verified then work must be duplicated. In a recent version of UPPAAL steps have been taken to reuse portions of the computed reachable state space [31].

A large part of the work UPPAAL must do in traversing (and computing) the state space during verification is the repeated application of clock constraints. To aid in the computation of the set of successor states an efficient data structure known as *difference bounded matrices* (DBM) is used for the representation and manipulation of clock constraints [32]. This canonical structure holds all possible constraints for any clock or pair of clocks. When computing the successor states it is important to be able to quickly determine the intersection between constraint regions. This structure is also used in KRONOS.

The description language also supports the modeling of systems with a "simple linear hybrid automata." This structure is a timed automata with clock values on the transitions that are not a fixed value, but are defined to be a clock interval with upper and lower bounds. This non-deterministic interval structure is then transformed into the standard timed automata supported by UPPAAL [28]. There is no specific support for clock intervals in the underlying symbolic representations used for model checking. The author does not make claims about the efficiency of the standard timed automata that results from this translation.

#### KRONOS

KRONOS is a tool for the verification of safety and liveness properties of real-time systems and the domain of timing analysis of hardware circuits. The system model is a set of concurrently operating timed automata with a finite set of real-valued clock variables. The values of the clock variables increase uniformly to denote the passage of time. KRONOS uses a timed extension of CTL, TCTL [33], as a means of formally describing the quantitative temporal properties of the timed-automaton model to be verified.

KRONOS uses symbolic representation methods very similar to those used in UPPAAL to attempt to control the state explosion problem. Instead of representing single states, a symbolic representation is used to represent a set of states. The set of states is represented by a system of linear constraints over the clocks of the timed automaton. These clock variables of the systems can take on any positive real value. A structure called a *region graph* is suited for representing finite portions of this infinite state space [34]. Sets of equivalent states are represented by nodes, or regions, of a region graph. Essentially, the sets of equivalent states, or regions, describes the unique *states* of the system for verification purposes. These regions can be manipulated to traverse the state space. The disadvantage to this approach is that the size of the region graph is exponential with respect to both the number of concurrently operation processes and also the number of clock variables present in the system. This region graph becomes quickly unmanageable. This approach is basically an enumeration of the state space.

To improve on this approach, KRONOS has implemented an on-the-fly approach to the exploration of the state space. In this approach, a symbolic graph called a *simulation graph* is constructed. This simulation graph is much smaller (because of its

implicit symbolic representation of the state space) than the region graph. The simulation graph only explicitly models the transitions between discrete states. The passage of time occurs implicitly inside the state nodes [34]. The verification algorithms perform a depth-first search of this simulation graph that is constructed "on the fly". A single stack is used to keep track of the current path of the simulation graph being explored. Using this method it is not required that the entire simulation graph be completely constructed in memory. Although the individual states of this graph represent a state set or region of the state space, a disadvantage to this method is that all simulation graph trajectories must be explored individually.

The cost of verification (size of state space) grows drastically as the number of system clocks increase. Another tool suite known as Optikron has been developed to reduce the number of clock variables of a timed automaton without changing its semantics [35]. Optikron can be used to reduce the complexity of the model before handing it off to the verification tool. Two main clock reduction techniques are used in Optikron. The first technique searches the model to detect *active* clocks – clocks that are necessary to produce the desired behavior of the system. If a clock is found to not be active then it can be safely removed without changing the system behavior. The second method works to detect clocks that are always the same for any location in the model. If a pair of clock variables is found to be the same value for all cases, then they can be collapsed into a single clock variable [36].

### Summary

The tools Uppaal and Kronos both verify systems using a fairly low-level timed automata model. Neither method has the facilities for modeling *system* level concepts

such as processors/processing elements, high-level model descriptions, etc. They are both for *design verification*. This work attempts to provide accurate *design and implementation verification*.

### **CHAPTER III**

### MODELS OF COMPUTATION

This chapter presents the models of computation used in this dissertation. A model of computation defines the interactions that may occur among components. In [37], Lee refers to a model of computation as "laws of physics" that govern component interactions. It is the programmer's model, or the conceptual framework within which larger designs are constructed by composing components.

The definitions of the existing FSMs, Statecharts, and Timed Automata are reviewed. A new statechart-like model, RScharts, is introduced. A timed extension of the RSchart model, named TRScharts, is also introduced. TRScharts extends the RSchart definition with the concept of states that have a finite, discrete duration. It was necessary to define these new models because the feature set and step semantics vary slightly from other defined statechart variations.

The dataflow model of computation is reviewed in a general sense. Note that the dataflow model of computation specific to this dissertation (Real-Time Dataflow) is introduced in Chapter V.

### Finite State Machines

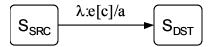

Finite state machines (FSMs) are used to represent dynamic systems where at each moment the system is considered to be in one of a finite number of unique states. When a state change occurs, the next state is chosen based on the system inputs and available transitions.

A finite state machine is a 4-tuple,  $R = \langle X, S, NS, S_0 \rangle$  where,

X is the input alphabet

S is the set of all states

NS: next state transition function,  $S \times X \rightarrow 2^S$

$S_0$  is the initial state

FSMs are used not only for hardware description for synthesis but can be used for specifying behavioral descriptions of any finite state system. This work will exploit the fact that the FSM model can be used to model non-deterministic behavior. A current *system state* composed of both a state and input label from the set S × X can map into two or more states allowing the possibility for multiple transitions to be enabled simultaneously from a single state. This allows the model to represent multiple behaviors from a single state and given input conditions. Both deterministic and non-deterministic FSMs can be represented in the form of a single Boolean function (the *next-state* transition relation). FSM visualizations used for system modeling are sometimes referred to as *state transitions graphs*.

### Statecharts

Large systems can require thousands of states to accurately model their operation. Using standard FSM models, these systems quickly become too cumbersome to comprehend. Most large systems naturally decompose themselves into concurrent behaviors. If these systems are modeled with a standard finite state machine (FSM), the number of states needed to represent the system behavior quickly explodes (known as the *state explosion* problem). Many languages have been developed to extend the basic FSM model to address this concern.

The most notable (and first developed) of these languages is the Statechart language [38]. Statecharts were developed by Harel for the specification of reactive systems (dominated by control logic) for use in the STATEMATE system, a commercial tool developed by I-Logix [39]. The Statechart language is a graphical language that extends the features of the traditional standard finite state machine with the concepts of hierarchy, concurrency, synchronous broadcast, and many other features.

The parallel composition of two state machines F and G will yield a system state space with the Cartesian product of these two state machines ( $|G| \cdot |H|$  total states). Providing support in the language to represent hierarchy and concurrency explicitly allows us to represent a complex state space in a compact manner to avoid the state explosion problems (at least in the representation) that can arise in normal FSMs. This is important since many systems have inherent concurrency in their operation that would be very difficult to capture, and certainly difficult to understand, using standard FSMs. Use of hierarchy promotes top-down design practices and allows for modeling of systems at varying levels of granularity (although statecharts have additional features such as interlevel transitions that somewhat work against these design principals).

Each state can be composed of several sub-states that either operate independently or sequentially. Using Statecharts to model a system can greatly reduce the number of states needed to graphically represent system behavior and make the model much easier to comprehend. Consider a Statechart model as shown in Figure 7. This statechart has four independently operating parallel state machines (S<sub>2</sub>, S<sub>3</sub>, S<sub>4</sub>, S<sub>5</sub>) each having three sub-states. This model has 18 total states, whereas an FSM model would require 81 individual states to express the same behavior. Note that this more compact representation represents the equivalent behavior of the potentially large flat FSM model.

Figure 7: Example statechart

Defining the semantics of statecharts boils down to defining the step semantics – exactly how the system transitions from one state to the next and the actions that may take place around this state change. In the original Statecharts language as defined in [38] by Harel, and used in STATEMATE, implements two types of step semantics. The first is an asynchronous time model where the system reacts (takes a step) whenever an external change occurs and repeatedly executes a step until the system reaches a steady state called a *stable configuration*. This series of steps is known as a superstep and appears as instantaneous operation to the user. Each superstep takes one unit of time. In this case the system semantics satisfy the *synchrony hypothesis*. The synchrony hypothesis states that the system is always faster than its environment [39]. The system reacts to each input individually and the response to the input is seen as instantaneous. The second is a synchronous time model where at each clock tick the system responds to

all external changes that have occurred since the completion of the previous step. The system only changes state at each clock tick.

Many variations of statecharts exist including a recent adoption of a statechart standard by UML [40]. Von der Beeck provided a good comparison of many (over 20) statechart variants in [41].

## **RScharts**

The variant of statechart used in this work known as Restricted Statecharts ("RScharts") is described below. The RScharts model features are very close to the basic Statechart features as defined by Harel in [38]. Some of the original Statechart features not supported are: history mechanisms and the use of global variables. The syntax of RScharts is specified below.

## Syntax

Formally, an RSchart is defined as  $ST = (S, T, E, S_0, Type, H)$  where,

S is a finite set of states, where each state, s (s  $\subseteq$  S), is declared as one of the three state types: {AND, OR, BASIC}

E is a finite set of events ( $e \subseteq E$ )

S<sub>C</sub> is a set of states that forms a valid state configuration.

$T\subseteq$  (  $S_C\times 2^E\to S_C\times 2^E$  ) is the finite, global state transition relation

$S_0$  is a set of initial states ( $S_0 \subseteq S$ )  $S_0$  forms a valid initial state configuration.

Type:  $S \rightarrow \{AND, OR, BASIC\}$  The state type mapping function.

$H: S \rightarrow S$  The state hierarchy function. If  $s' \subseteq H(s)$ , then s' is an immediate descendant of s. The function H describes a state tree hierarchy of the model.

*Root* is the state at the uppermost level in the state hierarchy (Root  $\subseteq$  S), Type(Root) = OR.

Each of the three states types of an RSchart is described below:

**AND States.** States of type AND enable modeling of concurrency by composing several simultaneously active sub-RScharts. AND states are parent states to sub-RSchart state machines that are concurrently active. These sub-RScharts may interact with each other via guarding conditions and events generated by other active components of the statechart. Immediate descendants of AND states must always be OR states. For a given s, if t Type(s) = AND, then t S't SH(s), Type (t) = OR.

**OR States.** States of type OR support the embedding of one RSchart inside another to provide hierarchy in the model. OR states have sub-states that are related to each other by an exclusive-or relationship. Only one state may be active at a time. Both AND states and OR states are referred to as "superstates".

**BASIC States.** States of type BASIC have no sub-states. For a given s, if Type(s)=BASIC, then H(s)= $\varnothing$ . The leaf states of an RSchart hierarchy must always be basic states. That is, if H(s)= $\varnothing$ , then Type(s) must be BASIC.

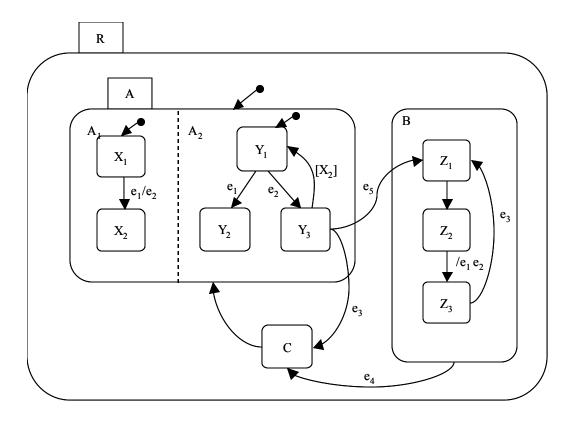

An RScharts model, at any instant, may have multiple active states (if concurrency is modeled by the use of one or more AND states). This aggregate current system "state" of an RSchart is known as a *state configuration*. A state configuration always contains the Root state of the statechart. A state configuration must contain

exactly one sub-state for each OR state and all sub-states for each AND state. A valid state configuration for the statechart in Figure 8 is: { Root, A, A<sub>1</sub>, A<sub>2</sub>, X<sub>2</sub>, Y<sub>3</sub> }. Figure 9 is a tree structure depicting the hierarchical structure of the statechart in Figure 8.

Figure 8: Example RSchart

Figure 9: Example RSchart hierarchy structure graph of Figure 8

Harel states that state configurations are "closed upwards". When a system is in any state, s, the configuration must also be in the parent state of s [39]. Note that, in reality, the set of BASIC states of a configuration are all that is needed to identify a state configuration. In Figure 8, for example, the set  $\{X_1, Y_1\}$  is sufficient to represent the initial state configuration. This minimal set will be referred to as a *basic configuration*. The current overall system "state" of the RSchart is composed of the currently active state configuration along with the set of events that are currently active. In this paper, we will refer to this global system "state" of the statechart as a *global configuration*. In Figure 8 a possible global configuration of the statechart is  $\{R, B, Z_3, e_1, e_2\}$ .

Initial states are shown graphically as a sourceless arrow pointing to a state to be identified as an initial state. Each superstate must have an initial state in its immediate sub-hierarchy identified. The Root state is, by default, an initial state. The RSchart in Figure 8 has an initial state configuration of  $S_0 = \{R, A, A_1, A_2, X_1, Y_1\}$ .