# TOWARDS DEVELOPING TOOLS AND TECHNOLOGIES FOR MODELING FAULTS IN LARGE SCALE, REAL TIME, REACTIVE EMBEDDED SYSTEMS

| ] | B | у |

|---|---|---|

|   |   |   |

# Shweta Shetty

Thesis

Submitted to the Faculty of the

Graduate School of Vanderbilt University

in partial fulfillment of the requirements

for the degree of

MASTER OF SCIENCE

in

**Electrical Engineering**

May, 2004

Nashville, Tennessee

| Approved: | Date: |

|-----------|-------|

|           |       |

|           | <br>  |

|           |       |

Dedicated to,

My parents

#### **ACKNOWLEDGEMENTS**

This research was sponsored by the National Science Foundation in conjunction with Fermi National Accelerator Laboratories, under the BTeV Project, and in association with RTES, the Real-time Embedded Systems Group. This work has been performed under NSF grant #ACI-0121658.

To start with I would like to thank Dr. Theodore Bapty my graduate advisor for his guidance and time, whenever I needed either. His advice has been most valuable throughout my academic period here in ISIS. I am greatly indebted to Dr. Sandeep Neema for giving me a chance to work in the BTeV project and his constant support and technical guidance were instrumental in keeping me motivated without loosing sight of the goal.

I cannot overemphasize my family's contribution in getting me where I am today.

I am grateful for every little word of advice, encouragement and concern they have spoken for years.

Finally I would like to thank all my team members and also the folks who are actively involved in this project for being there for me whenever I needed their help.

# TABLE OF CONTENTS

|                                        | Page |

|----------------------------------------|------|

| DEDICATION                             | ii   |

| ACKNOWLEDGEMENTS                       | iii  |

| LIST OF TABLES                         | vi   |

| LIST OF FIGURES                        | vii  |

| LIST OF ABBREVIATIONS                  | ix   |

| Chapter                                |      |

| I. INTRODUCTION                        | 2    |

| Traditional Fault Tolerance Strategies | 3    |

| Problems With The Traditional Approach |      |

| Fault Mitigation Design Methodologies  |      |

| Problem Statement                      | 7    |

| II. BACKGROUND AND LITERATURE SURVEY   | 9    |

| Models of Computations                 | 9    |

| Finite State Machines                  |      |

| Discrete-Event Systems                 | 13   |

| Petri Nets                             | 14   |

| Data Flow Graphs                       | 15   |

| Results Of The Survey                  |      |

| Real Time Embedded System Design Tools |      |

| MetaH                                  |      |

| PTOLEMY                                | 22   |

| III. BTeV TRIGGER SYSTEM OVERVIEW      | 25   |

| BTeV Trigger Architecture              | 27   |

| DSP Network                            |      |

| Buffers And Switches                   |      |

| Proposed Solution                      |      |

| Summary                                |      |

| IV. MODELING ENVIRONMENT               | 36   |

| Prototype Overview                     | 36   |

|      | BTeV Paradigm                                  | 39 |

|------|------------------------------------------------|----|

|      | Mapping of Prototype into Modeling Environment |    |

|      | Application Dataflow                           |    |

|      | Hardware Resource Library                      |    |

| V.   | FAULT MITIGATION LANGUAGE                      | 45 |

|      | Requirements                                   | 45 |

|      | User Defined Mitigation Strategies             | 46 |

|      | Message Structure                              |    |

|      | Input and Output of the Fault Manager Machine  | 49 |

|      | Various Features Of State – Machine Language   | 52 |

|      | Standard State Machine Implementation          | 54 |

|      | Nested Switch Statement                        | 55 |

|      | State Table                                    | 57 |

|      | Summary                                        | 58 |

| VI.  | CASE STUDY                                     | 59 |

|      | Failure Scenarios                              | 60 |

|      | Case 1 – Supercomputing 2003 Implementations   | 60 |

|      | Semantics                                      | 69 |

|      | Case 2 – General Fault Scenario                | 69 |

|      | Fault Manager Synthesis Algorithm              | 71 |

|      | Evaluation Of The Case Study                   | 74 |

| VII. | CONCLUSIONS AND FUTURE WORK                    | 76 |

|      | Conclusions                                    | 76 |

|      | Future Work                                    |    |

| REFE | RENCES                                         | 80 |

# LIST OF TABLES

| Table |                                             | Page |

|-------|---------------------------------------------|------|

| 1.    | Strengths and Weakness of different models. | 17   |

# LIST OF FIGURES

| Figure |                                                                  | Page |

|--------|------------------------------------------------------------------|------|

| 1.     | Classification of Error, Faults and Failure                      | 4    |

| 2.     | State Transition diagram and State Transition Table              | 11   |

| 3.     | MetaH Architecture                                               | 20   |

| 4.     | Design Methodology Management using Ptolemy [31]                 | 23   |

| 5.     | BTeV Detector                                                    | 26   |

| 6.     | The Trigger Architecture <sup>1</sup>                            | 27   |

| 7.     | Model Based Approach to Fault- Mitigation                        | 31   |

| 8.     | Design flow from metamodeling to application synthesis using GME | 32   |

| 9.     | Prototype Software Application                                   | 37   |

| 10.    | Hierarchical Fault Mitigation Runtime Environment                | 39   |

| 11.    | Software Component                                               | 41   |

| 12.    | Hardware Component                                               | 43   |

| 13.    | State Machine paradigm                                           | 48   |

| 14.    | Message Structure                                                | 49   |

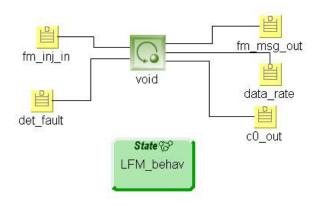

| 15.    | Input and Output of State Machine                                | 50   |

| 16.    | Example FSM for Standard Implementation Techniques               | 55   |

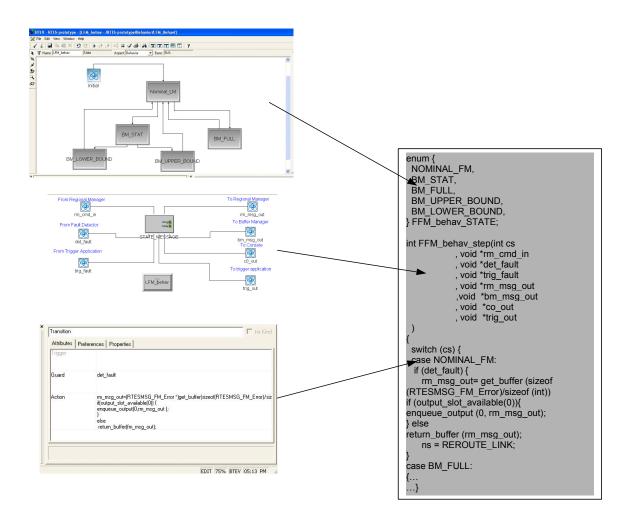

| 17.    | Switch Case Implementation                                       | 56   |

| 18.    | State Table Representation                                       | 57   |

| 19.    | Worker Node                                                      | 61   |

| 20.    | Local Manager data ports                                         | 62   |

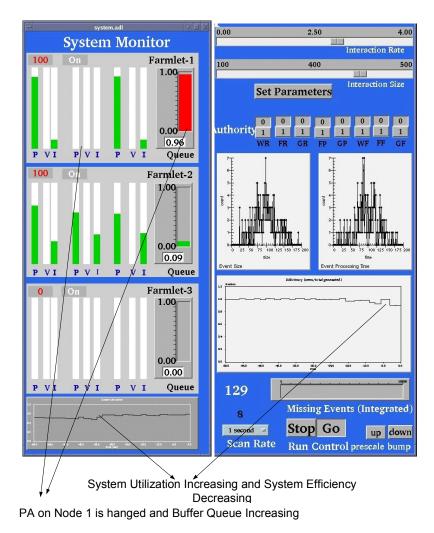

| 21.    | User Interface Showing the System Information                    | 63   |

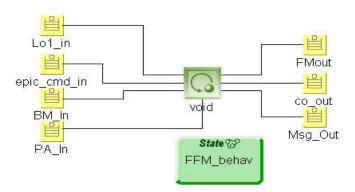

| 22.    | Farmlet Manager Data ports                                       | 64   |

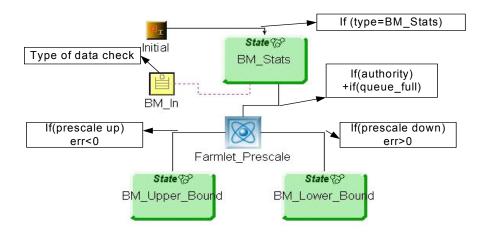

| 23. | State Diagram for Prescale Behavior                              | 65 |

|-----|------------------------------------------------------------------|----|

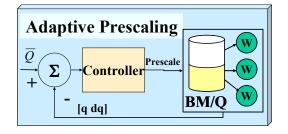

| 24. | Adaptive Prescaling Using PD Algorithm                           | 65 |

| 25. | Values of Proportional and Derivative constants                  | 66 |

| 26. | Equation for calculating error                                   | 66 |

| 27. | System Information showing the values of prescale and efficiency | 67 |

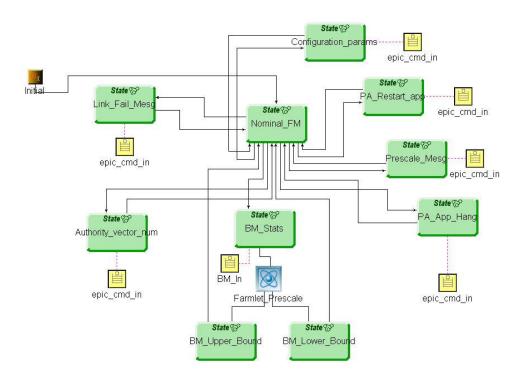

| 28. | Complete Behavior.                                               | 68 |

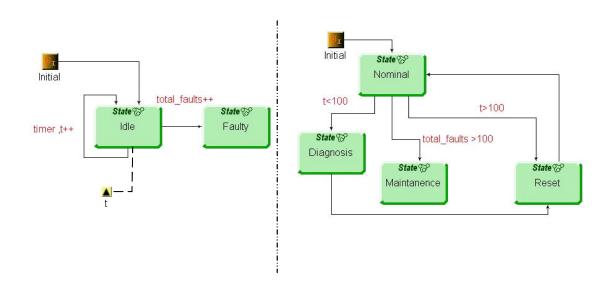

| 29. | General Example showing the fault mitigation language            | 70 |

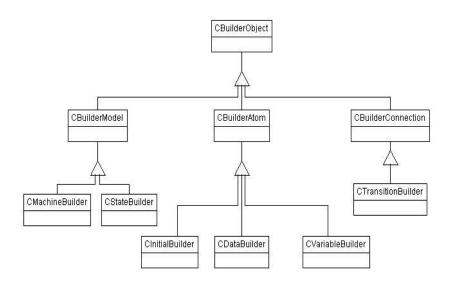

| 30. | Class Diagram of BTeV specific classes                           | 72 |

| 31. | Mapping of Generated code and the models                         | 74 |

#### LIST OF ABBREVIATIONS

BTeV -B physics at the TeVatron.

FNAL -Fermi National Accelerator Laboratories .

RTES- Real-Time Embedded Systems

DSP – Digital Signal Processing

FSM - Finite State Machine.

CFSM - Codesign Finite State Machine.

HPN - Hierarchical Petri Nets.

SDF - Synchronous Data Flow.

ADF - Asynchronous Data Flow.

COSYMA - COSYnthesis of eMbedded Architectures.

DFG - Data Flow Graph.

MIC - Model Integrated Computing.

GME - Generic Modeling Environment.

OCL - Object Constraint Language.

COM - Component Object Model.

API - Application Programming Interface.

BON - Builder Object Network.

XML - eXtensible Markup Language.

UML –Unified Modeling Language

TMR – Triple Modular Redundant

## CHAPTER I

## **INTRODUCTION**

Research in fault-tolerant distributed computing aims at making distributed systems more reliable by handling faults in complex computing environments. Moreover the increasing dependence on well designed and well-functioning computer systems has led to an increasing demand for tools for building dependable systems, systems with quantifiable reliability properties.

Arguably dependability is one of the most crucial design considerations for a majority of embedded systems. Often in this class of systems the term "the system crashed" is not just a metaphor, it may have real and physical consequences. Even with best practices and careful design decisions, the growing scale and complexity of embedded systems makes it impossible to perform an exhaustive coverage that assuredly scrubs out each potential failure source. Potential failures could arise from hardware, or software, or the physical processes with which the embedded system has to interact, or a combination of any of these. Furthermore, extended operational life-cycle of the embedded system introduces the fatigue factor also as a possible source of failure. Given the myriad potential fault sources – some of which may not even be identifiable, and the inability to prevent those failures from occurring, the only possible mechanism of introducing dependability in a system is by means of *fault tolerance* or *fault mitigation*.

# <u>Traditional Fault Tolerance Strategies</u>

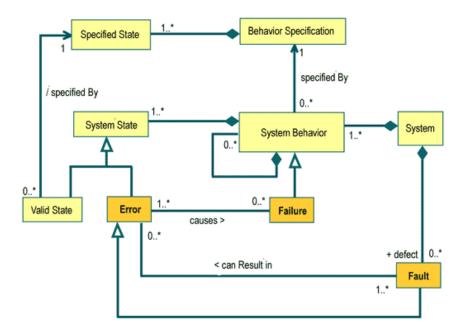

Fault Tolerance is the ability of a system to perform its function correctly even in the presence of internal faults. The benefits of fault tolerance are usually advertised as improving dependability –the amount of trust that can justifiably be put in a system. Normally, dependability is defined in statistical terminology, stating the probability that the system is functional. The metric provides the expected service at a specific point in time. There is considerable ambiguity in the literature on the meaning of some central terms like fault and failure. Cristian [1991] [1] remarks that "what one person calls failure, a second person might call fault, and the third person might call error". The term fault is usually used to name a defect at the lowest level of abstraction, e.g., a memory cell that always returns a value 0 [Jalote 1994]. A fault may cause an error, which is a category of the system state. An error, in effect, may lead to a failure, meaning that the system deviates from its correctness specification. In other words, a fault is the root cause of a failure. Thus, an error is merely the symptom of a fault. A fault may not necessarily result in an error, or the same fault may result in multiple errors. Similarly, a single error may lead to multiple failures. These basic concepts are illustrated using Unified Modeling Language (UML) class diagram in Figure 1.

Traditionally faults were handled by describing the resulting behavior of the system and grouped into a hierarchic structure of fault classes or fault models [1]. Well known models are the *crash* failure models (in which processors simply stop executing at a specific point in time), *fail-stop* (in which a processor crashes, but this may be easily detected by its neighbors), or *Byzantine* (in which processors may behave in arbitrary ways).

Figure 1 Classification of Error, Faults and Failure

The fault tolerant research community has been able to produce some useful techniques – such as warm / cold / hot replication, active or passive replication, check-pointing, heartbeat, n-way redundancy with or without voting to name a few. At the heart of all the fault tolerance techniques is some form of masking redundancy. This means that components that are prone to defects are replicated in such a way that if a component fails, one or more of the non-failed replicas will continue to provide service with no appreciable disruption.

**Replication Checks**: In this case, multiple replicas of a component perform the same service simultaneously. The outputs of the replicas are compared and any discrepancy is an indication of an error in one or more components. A particular form of this that is used in hardware is called triple-modular redundancy (TMR), in which the output of three independent components is compared, and output of the majority of the components is

actually passed on. In software, this can be achieved by providing multiple independently developed realizations of the same component. This is called N-version programming. This method of course works well for small systems where hardware is cheap and memory is plentiful. In high performance parallel systems, fault tolerance using conventional redundancy methods can be extremely costly, as system size and complexity increase.

# <u>Problems With The Traditional Approach</u>

The traditional approach has been around for a while and is still in practice. However, this approach is not suitable for many cost-sensitive or large scale systems. It is well understood that the software development for real time embedded systems is a difficult undertaking. In addition to the functional and temporal correctness, reliability is a key design factor. Certain classes of reliable RT systems, such as a high energy physics trigger systems employ very large numbers of processors that must operate consistently over several months. N-mode redundancy is not an option due to scale of the system and cost constraints. A "reasonable behavior" is expected from these systems when the hardware or the software components fail. There is not a single answer to how the system should react when fault occur, rather behavior is dependent on the application or mode of operation. In the class of systems of interest, namely large-scale real-time embedded systems, often different levels of failures and thereby reduced level of functionality are acceptable under certain circumstances. The overarching requirement is that the failures should not have a cascading effect that some level of functionality of the system should remain. Within this umbrella of non-cascading failures, the specific response to failures is often user-defined and situation dependent. This response could range from a simple

notification on an operator interface, to active load shedding (with due logging of system state), to processor resets/test and hot-spare failovers. Thus, in the domain of very large parallel systems, designers of embedded systems rarely have the luxury to employ such hardware-intensive tactics. In such cases, software plays an important role in achieving fault tolerance, but this can severely complicate implementation. Maintaining the high quality in software-adaptive, fault tolerant embedded systems is only possible with the assistance of advanced software tools. These tools can shift the burden of the design away from human. The tools should take the form of a highly customizable fault-mitigation framework that includes high level design tools and runtime support infrastructure.

# Fault Mitigation Design Methodologies

As we mention above, the class of systems of interest for this research is very large scale real time embedded systems which have a need for a customizable fault mitigation methodology. There are two minimum requirements of such a system by the users

- 1) The system should not fail abruptly

- 2) Faults should not have a cascading effect.

However, between these two absolutes, there is a diverse range of specifications for responses to different kinds of faults. For example, if for some reason an algorithm residing on a processor terminates without finishing the computation due to either hardware, or software fault, the designer may require the algorithm to be computed in an n-mode redundancy mode or check-pointed for a restart, or even a notification that is duly logged may suffice. Thus, a simple notification mechanism combined with an

algorithm restart is sufficient to meet the dependability specifications in this case. On the other hand, a repeated recurrence of algorithm failure on the same processor might require a fault response in the form of a processor reset followed by diagnostic session. In this case some amount of hardware redundancy is required. This diversity of fault responses demonstrates the need for a highly flexible and customizable fault tolerance framework. This framework should allow the users of the system, to specify fault responses, in an abstract (high-level) yet precise form (i.e. fault response specifications). These specifications could then be used to automatically customize the fault-tolerance infrastructure to suit their application and system requirements. With this motivation we have been developing high-level design tools, and a highly flexible fault-tolerance runtime infrastructure to construct systems – specifically, Fermi Lab's BTeV trigger system –that falls into the class of large scale real time embedded system.

## **Problem Statement**

The aim of this thesis is to develop a model based tool set for software based fault mitigation strategies and to apply these tools within the framework of BTeV. The first step comprises developing a domain-specific modeling environment for fault-adaptive applications implemented on large-scale parallel systems. The next step is to integrate the modeling environment with the existing software infrastructure to create a heterogeneous environment for the design of embedded application. The integrated environment should allow the users to specify modular system design with alternative implementations.

The tools should have the capability to interpret the system models and generate code for various fault mitigation strategies and also it should have the ability to synthesize low-level programming artifacts from the higher-level abstractions, alleviating

the system developer from the burden of constructing low-level artifacts, ensuring consistency with the higher-level abstractions.

This thesis presents the tool rationale, implementation strategy, and a case study of the approach. Chapter II presents a survey of different relevant models of computations (MOCs) and other real time embedded system design tool. Chapter III describes the BTeV trigger system and the modeling paradigm for hardware/software. Chapter IV presents a case study to validate the tools and design philosophies and in Chapter V a detailed explanation of the fault mitigation language and formalisms and the conclusions are drawn in Chapter VI.

#### CHAPTER II

#### BACKGROUND AND LITERATURE SURVEY

# Models of Computations

The specification process is a fundamental aspect of system design. We advocate using an unambiguous formalism to represent design specification and implementation choices. These formalism are often called the *Model of Computation (MOC)*. There are several models of computation that have been specified and used in embedded systems. A MOC is composed of a description mechanism (syntax) and rules for computation of the behavior given the syntax (semantics). Models of computation can serve different domains or aspects of a specific system. For example, some MOC's are suitable for describing complicated data transfer functions and completely unsuitable for complex control, while others are designed with complex control in mind. A MOC is typically realized (implemented in practice) by a particular language and its semantics. Multiple Models of Computation can be used in any particular system, each describing different aspects of the computation. Here, we survey several MOC's that are appropriate for applications like the BTeV Trigger.

#### Finite State Machines

State Machine based specification methodologies are an efficient and popular way to describe and analyze event-driven systems. System behavior is represented by a directed graph, consisting of a finite set of conditions, called **states** and paths between the states, called **transitions**. Finite State Machine (FSM) is a well-established

representation. It can be defined as a model of computation consisting of a set of **states**, a **start state**, an **input alphabet**, and a **transition function**, which maps input symbols and current states to a next state. This representation is useful in describing applications that are tightly coupled with the environment. It is also suited for control-dominated and reactive applications. With basic FSM's however, concurrency is not easily captured. Representing concurrent states results in the exponential growth in the number of states with linear increase in degree of concurrency. This problem is also known as the state space explosion problem. Furthermore, small changes to the requirements may result in large changes to the corresponding FSM. In order to overcome various weaknesses of the classical FSM a number of extensions such as hierarchy and concurrency have been developed. A few such variants are discussed [2].

A classic state machine is basically a quintuple of the form:

$$FSM M: = (Q, \sum, \Delta, \partial, q_0)$$

where

- Q is a finite set of states

- $\sum$  is a set of input events

- $\Delta$  is a set of output events

- $\delta: Q \times \Sigma \rightarrow Q \times \Delta$  is the state transition function

- $q_0 \in Q$  is the initial state

An example of simple state machine is:

$$M = (\{A, B\}, \{a, b\}, \{\varepsilon, u, v\}, \delta_{M, A})$$

(2)

$$\delta_{\mathbf{M}} = \{ (\mathbf{A}, \mathbf{a}) \rightarrow )(\mathbf{A}, \varepsilon), (\mathbf{A}, b) \rightarrow (\mathbf{B}, u), (\mathbf{B}, a) \rightarrow (\mathbf{A}, v), (\mathbf{B}, b) \rightarrow (\mathbf{B}, \varepsilon) \}$$

(3)

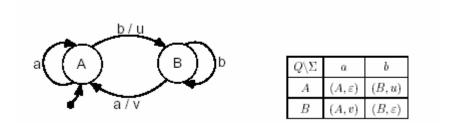

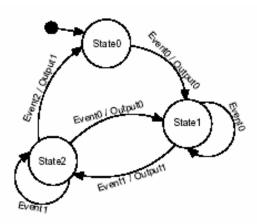

There are chiefly two options for the representation of a state transition function  $\delta$ . The graphical depiction on the basis of a state transition diagram as shown in Figure 2 is the preferred way, because the behavior is readily apparent from the diagram. All modern state machine supporting software tools provide a graphical design environment for FSMs. Alternatively, a state transition table (table in Figure 2) can be used to represent the transition function of a particular state machine.

Figure 2 State Transition diagram and State Transition Table

Mealy and Moore Automata are just two of the different ways in which state machines can be interpreted. The major difference in the two methods is in the execution time of the output events. Both architectures split a state transition function into a pure transition function and an additional output function. Therefore, a Mealy as well as a Moore automaton is defined as a sextuple:

$$FSM M: = (Q, \sum, \Delta, \delta, \mu \setminus \lambda, q_0)$$

where

- Q is a finite set of states

- $\sum$  is a set of input events

- $\Delta$  is a set of output events

- $\delta: Q \times \Sigma \rightarrow Q$  is the state transition function

- $\mu: Q \rightarrow \Delta$  is the Moore output function

- $\lambda$ ,:  $Q \times \sum \rightarrow \Delta$  is the Mealy output function

- $q_0 \in Q$  is the initial state

In case of a Mealy automaton, output events are associated with transitions and depend on the current state and current input event. Based on these semantic, the Mealy approach assumes that output actions take no time to execute, because a system is not in a well defined state while outputs are performed. The Moore architecture avoids the so called zero time assumption. Here, output events are associated with states. The system state is always well defined during action execution. Both automata are mathematically equivalent and one always can be transformed into the other. As a rule, a Mealy state machine interpretation requires fewer states, because a Moore automaton must use different states to represent conditions in which different actions are performed

Codesign Finite State Machine (CFSM) is another model based on the FSM. It is intended to describe embedded applications with low algorithmic complexity. Both hardware and software can be depicted using this model of computation. It can be used to partition and implement applications. The basic communication primitive is an event. The behavior of the system is defined as a sequence of events. The events are broadcast and have zero propagation time. This model of computation is used as an intermediate representation that high-level languages can map to [2][3].

Statecharts by Harel [4] is another extension of FSMs that provides three major facilities, namely: hierarchy, concurrency and communication. Statecharts are high-level Finite State Machines having AND and OR states. The AND states primarily achieve

concurrency while the OR states are for representing hierarchy. Communication is based on events that are broadcast instantaneously. This representation is well suited for large and complex reactive systems.

# Discrete-Event Systems

Systems having discrete states and driven by events over a period of time are referred to as Discrete-Event Systems [5]. A discrete event system (DES) is a dynamic, asynchronous system, where the state transitions are initiated by events that occur at discrete instants of time. Typical examples of DES are: flexible manufacturing systems, telecommunication networks, traffic control systems, multiprocessor operating systems and logistic systems. These systems are asynchronous in nature and react to discrete events over time. An event is considered instantaneous, that is, the transition and action due to the event occur with no execution time. Although DES lead to a nonlinear description in linear algebra, there exists a subclass of DES for which this model becomes "linear" when we formulate it in the max-plus algebra.

Signals form the primary method of communication between tasks. They consist of a set of events over time. The events are time stamped and are sorted and processed in chronological order. Discrete-Event Systems are backed with formal mathematical description [6] that allows modelers to do formal verification and build deterministic systems. Though these systems are good for real time applications the primary disadvantage is the computational cost of sorting the events globally to maintain the chronology.

#### Petri Nets

Petri-Nets [7] methods are graphical notations with a solid mathematical foundation. They can be used in a number of different ways to represent computer based systems, especially those concerning concurrency, distribution and non-determinism. The concept was invented by Carl Adam Petri in 1962 and has been proposed for a wide range of applications including performance evaluation, communication protocols, and multiprocessor design. A Petri-Net is described as a 5-tuple,

PN= {P, T, F, W, Mo} where: (5)

$$P = \{p1, p2, p3, ..., pm\}$$

is a finite set of places

$$T = \{t1, t2, t3, ..., tm\}$$

is a finite set of transitions

$$F \text{ is a subset of } (P \times T) \cup (T \times P)$$

is a set of arcs giving flow relations

$$W: F \to \{1, 2, 3, ...\}$$

is the weight function

$$Mo: P \to \{0, 1, 2, ....\}$$

is the initial marking

The places hold tokens and a transition can occur if the number of tokens required for the transition is present in the place. A transition removes a specific number of tokens from its source and adds tokens to the destination. A snapshot of places with the number of tokens describes the state of the system.

Petri nets are a promising tool for describing and studying systems that are characterized as being concurrent, asynchronous, distributed, parallel, nondeterministic, and/or stochastic. As a graphical tool, Petri nets can be used as a visual-communication aid similar to flow charts, block diagrams, and networks. In addition, tokens are used in these nets to simulate the dynamic and concurrent activities of systems. As a mathematical tool, it is possible to set up state equations, algebraic equations, and other

mathematical models governing the behavior of systems. The primary feature of Petri Nets is its concurrent and asynchronous nature. Along with concurrency and asynchronicity, there are a number of mathematical analyses that can be performed on Petri Nets. The lack of hierarchy makes Petri Nets difficult to be use for large systems.

Hierarchical Petri Nets (HPNs) [8] have been developed to mitigate the complexity of a flat representation. HPNs are modeled by bipartite directed graphs with inscription on the nodes and edges. There are two types of nodes, transitional nodes that represent activity and places that represent data or the state of the system [2]. This approach extends the Petri Net semantics with hierarchy making it suitable for large and complex systems.

# Data Flow Graphs

The classical programming structure of computer-based systems is control dominated. An alternative approach is data-dominated where the control flow is determined by availability of data. These systems have nodes describing computation and edges between nodes denoting a data path. Here the control is based on the availability of data. In other words the scheduling of the computation is tied to the availability of data. If a node has sufficient data available on its incoming edges then it is ready to fire and will use the input data to generate output data. Transfer of data between computational modules is typically done via buffers. This allows the tasks to run independently.

Various flavors of data flow are seen in literature. The two popular and distinct ones are Synchronous Data Flow (SDF) and Asynchronous Data Flow (ADF). In SDF the number of token produced and consumed is fixed and must be known at the system design stage. This requirement allows the SDF to be statically scheduled [9] and

optimized for minimum buffers. The ADF is defined as a data flow graph with unbounded buffers where the computations can produce and consume variable number of tokens. Since the consumption and production of tokens can change at runtime, the ADF cannot be scheduled statically and hence, it has a greater run-time cost. However, it is more flexible than the SDF and can represent the majority of systems. Similarly, in hardware, structural description is widely used. The structural layout of the target DSP hardware is data driven and on a closer look it is very similar to an unbuffered asynchronous data flow. It is defined in a variant of ADF with the buffer length being zero. In other words there is no buffering of data.

# Results Of The Survey

Most of the models of computation discussed are suitable for either data-dominated or control-dominated systems. SDF and ADF methods are good for the signal-processing domain. Similarly FSM is useful in representing control-dominated systems. There is no single model well suited for both control and data requirements. Thus, depending upon the target application area, the model of computation needs to be chosen. Composing different models of computation is also worth considering [22][23].

Table 1 Strengths and Weakness of different models.

| Model                       | Strengths                            | Weaknesses                    |

|-----------------------------|--------------------------------------|-------------------------------|

| Finite State Machine        | Good for sequential control          | No code reuse, application    |

|                             | Can be made deterministic            | specific.                     |

|                             | Maps well to hardware and software   |                               |

| <b>Discrete Events</b>      | Good for digital hardware            | Expensive to implement in     |

|                             | Global time                          | software                      |

|                             | Can be deterministic                 |                               |

| Synchronous/Reactive        | Good for control-intensive systems   | Computation-intensive         |

| Model                       | Tightly synchronized                 | systems are over specified.   |

|                             | Deterministic                        |                               |

|                             | Maps well to hardware and software   |                               |

| Dataflow                    | Good for signal processing           | Control-intensive systems     |

|                             | Loosely synchronized                 | are hard to specify.          |

|                             | Deterministic                        |                               |

|                             | Maps well to hardware and software   |                               |

| Communication               | Models resource sharing well         | Some systems are over         |

| <b>Sequential Processes</b> | Partial-order synchronization        | synchronized and difficult to |

|                             | Supports naturally non-deterministic | be made deterministic.        |

|                             | interactions                         |                               |

# Real Time Embedded System Design Tools

Many Computer Aided Software Engineering tools (CASE) are available to assist the developers with the software development process. Since the early days of writing software, there has been an awareness of the need for automated tools to help the software developer. Initially the concentration was on program support tools such as translators, compilers, assemblers, macro processors, and linkers and loaders. However, as computers became more powerful and the software that ran on them grew larger and more complex, the range of support tools began to expand. In particular, the use of interactive time-sharing systems for software development encouraged the development of program editors, debuggers, code analyzers, and program-pretty printers. The first generation of CASE tool developers concentrated to a large extent on the automation of isolated tasks such as document production, version control of source code, and design method support. While successes have been achieved in supporting such specific tasks, the need for these 'islands of automation' to be connected has been clearly recognized by many first generation CASE tool users. For example, a typical development scenario requires that designs be closely related to their resultant source code, that they be consistently described in a set of documentation, and that all of these artifacts be under centralized version control. The tools that support the individual tasks of design, coding, documentation, and version control must be integrated if they are to support this kind of scenario effectively.

In fact, such tools are more often used as components in a much more elaborate software development support infrastructure that is available to software engineers. A typical CASE environment consists of a number of CASE tools operating on a common

hardware and software platform. Also note that there are a number of different classes of users of a CASE environment. Some users, such as software developers and managers, wish to make use of CASE tools to support them in developing application systems and monitoring the progress of a project. On the other hand, tool integrators are responsible for ensuring that the tools operate on the software and hardware platform available, and the system administrator's role is to maintain and update the hardware and software platform itself.

Software developers, tool integrators, and system administrators interact with multiple CASE tools and environment components that form the software and hardware platform of the CASE environment. It is these interactions among the different CASE environment components and between users and those components which are the key elements of a CASE environment. In many respects the approach toward the management, control, and support of these interactions distinguishes one CASE environment from another. Hence, we can define a CASE environment by emphasizing the importance of these interactions:

"A CASE environment is a collection of CASE tools and other components together with an integration approach that supports most or all of the interactions that occur among the environment components, and between the users of the environment and the environment itself."

This section reviews the existing research and tools for co-design for real time embedded systems.

## MetaH

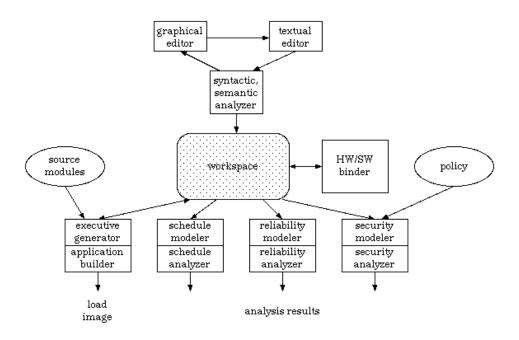

MetaH is a language and toolset for developing reliable, real-time multiprocessor avionics system architectures. It is also used for system analysis and integration as illustrated in Figure 3. It is a product of Honeywell and is a research prototype tool.

Figure 3 MetaH Architecture

MetaH specifies how software modules developed in a variety of styles are composed together with hardware objects to form complete system architecture. MetaH exhibits elements of real time process and concurrent state machine styles. MetaH specifications allow developers to compose software objects such as subprograms, packages and processes and hardware objects such as memories and processors. Hierarchical specification is supported, where macros and modes hierarchically combine software objects, and systems hierarchically combine hardware objects. MetaH allows

computer system engineers to integrate the source modules for all the various functional subsystems to form the final real-time, fault-tolerant, securely partitioned multi-processor system.

Three major classes of features distinguish MetaH from existing approaches to designing and integrating software using CASE tools and real-time operating systems.

- 1. MetaH specifications can be used to drive automatic software and system integration. Users do not need to design and hand-code configuration-specific sequences of calls to the various application modules and real-time operating system services. This reduces development effort and reduces defects in the code that integrates the application modules. Because the integration code is automatically generated, it is possible to rapidly reconfigure systems. Finally, static analysis by the tools allows many operations to be preplanned at development time rather than dynamically computed at run-time, which can significantly reduce on-board code size and overhead.

- 2. MetaH specifications can be subjected to formal analysis. Partial MetaH specifications can be partially analyzed, which supports design trade-off studies beginning very early in the development process. The co-generation of code and analytic models from a common specification provides high assurance that the analysis results accurately predict and bound final implementation behavior. The accuracy of analysis results can be relied upon during design trade-offs, and analysis results can be used in the V&V process.

- 3. The MetaH architecture specification language includes as part of its definition a discussion of the coding guidelines used for source modules. These guidelines

together with the MetaH language features define a set of common software/software and software/hardware interface mechanisms. Source modules can thus be more independent of the application, hardware and software context in which they are used. MetaH supports increased reuse of source modules. It also allows system architectures to be rapidly reconfigured to adapt to changing hardware and functional requirements without making changes to application source modules.

MetaH allows a specification of system components and connections, and attributes of those components and connections that are relevant to real-time, fault-tolerant, secure partitioning, and multi-processor aspects of an application. The kinds of objects in a MetaH specification can be divided into lower-level objects that describe source code modules (e.g. subprograms, packages) or hardware elements (e.g. memories, processors); and higher-level objects that specify how previously declared objects may be combined to form new objects (modes, macros, systems, applications). The language has both a textual and a graphical syntax, and the tools allow a specification to be viewed and edited interchangeably in either format.

The release toolset includes targets to a portable Ada 95 configuration (the MakeH build scripts use the GNAT toolset), and to single processor 960EXV and single and dual-processor 960CVME configurations (i80960MC processors using the Tartan Ada toolset and protected memory run-time).

### **PTOLEMY**

Ptolemy is a project dedicated to modeling, simulation and design of real-time, embedded applications started in 1990 at University Of California at Berkeley with focus

on component-based design. The philosophy of this project is centered on using different models of computation and developing an environment that allows the mixing of these models of computation to create a heterogeneous application [30].

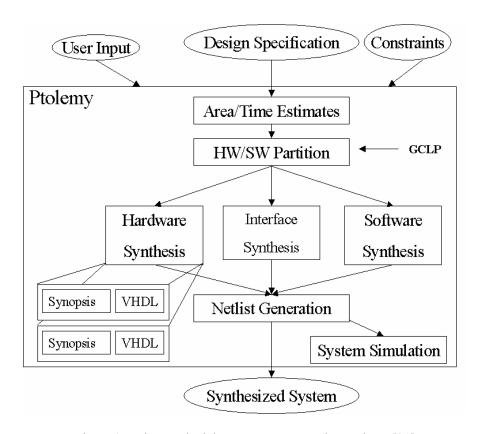

The primary aim of the Ptolemy project is to build a framework for modeling, designing and development of embedded applications. Figure 4 shows the design management strategy proposed by the Ptolemy project. Design starts with application specification using different models of computation and constraints. Different tasks of the system are evaluated and estimates are drawn. These estimates decide the hardware and software partition of the application. This is followed by hardware and software synthesis and verification. The final stage is the integration and system wide simulation [31].

Figure 4 Design Methodology Management using Ptolemy [31]

A Java-based framework called Ptolemy II has been developed that implements the project ideas. The framework has an environment for the simulation and prototyping of heterogeneous systems. It is an object-oriented system allowing interaction between diverse models of computation. The Ptolemy software is extensible and publicly available. It allows experimentation with various models of computation, heterogeneous designs and co-simulation. The primary feature of Ptolemy is the facility to compose various models of computation. Some of the models of computation supported by Ptolemy are hierarchical finite state machine, data flow graphs, discrete-event and synchronous/reactive. After specifying the application using heterogeneous models, the next step is to partition the application. This is done using different partitioning algorithms like GCLP [29]. Ptolemy facilitates mixed mode system simulation and synthesis. Software synthesis is supported for various models of computation along with support for composing these models. Hardware portions of the application are synthesized to VHDL. A register transfer level simulator (THOR) has also been added for simulating hardware applications [30].

Other key features of the project are the representation of modern theories in a block diagram specification, modular approach, a mathematical framework for comparison between models of computation and simulation and scheduling of complex heterogeneous systems [30].

#### **CHAPTER III**

#### BTeV TRIGGER SYSTEM OVERVIEW

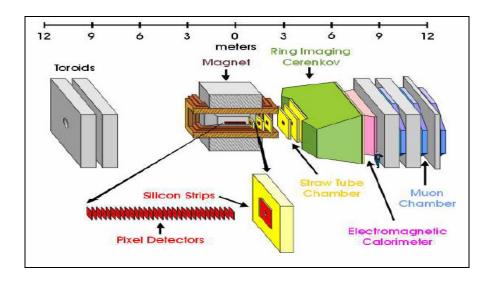

At Fermi National Accelerator Laboratory in Chicago, high energy physicists conduct experiments using massive facilities to delve into the basic composition of matter. The objective of the BTeV experiment is to search for charm charge-particle (CP) violations, mixing, and rare decays, as well as take measurements of beauty CP violation and rare decays [9]. The physicists expect to explain the large discrepancy between matter and anti-matter in the universe with such experiments. In these experiments, a particle accelerator called the Tevatron, applies enough energy to accelerate protons and anti-protons up to relativistic speeds. Packets of these particles rotate around a 1 mile diameter ring with particles and anti-particles moving in opposite directions. At specific locations within the ring, called the detector stations, the packets collide where collisions breaking the particles into the basic components of matter, or quarks [10]. Figure 5 shows a view of the equipment used to detect these basic particles.

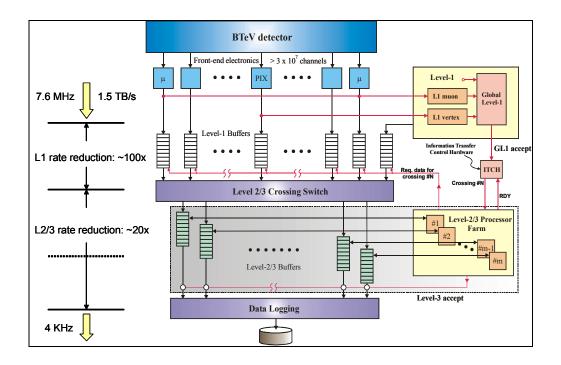

The accelerator is set up so that the collisions occurs every 135 nanoseconds. The sub-particles, product of the collisions, are measured by a set of planes of detectors, giving a 3-dimensional dataset. Each dataset consists of 200 KB of data. The aggregate raw data rate exceeds 1.5 TB per second. Most of these collisions result in well-known components, and are uninteresting to the physicists. Interesting products of collisions occur remarkably infrequently. In order to get sufficient data (on the order of 100 events), the experiments must run days or even months at a time.

Figure 5 BTeV Detector

Clearly, the aggregate data rate is too high to blindly record all data. Instead, algorithms, called Triggers, must be executed online to dynamically compute a keep/discard decision. These algorithms necessarily must be computed in real-time, although significant queuing is typically available. Distributed and concurrent computing solutions are necessary in order to perform the trigger algorithm in real-time. It is estimated that ~ 2500 front-end current-generation DSP processors and ~ 2500 general-purpose processors will be required. The primary focus of our research collaboration, which is known as the Real-Time Embedded Systems (RTES) group within the BTeV experimenters' community, is with the Trigger algorithm and its fault-tolerant execution. Next we provide an overview of the planned architecture for the trigger implementation.

Figure 6 The Trigger Architecture <sup>1</sup>

# BTeV Trigger Architecture

Functionally, the trigger spans three different levels. L1 is the first-level of trigger system responsible for detecting secondary vertices in a 3-dimensional data set, and rejecting non-interesting data-sets [15], with a reduction order averaging ~100:1.

L2 is the second level of the trigger algorithm. It does a refined tracking and vertex cut [34], with a reduction order of ~5-10:1. L3 is the third and final level of the trigger algorithm responsible for a complete event. L3 has a reduction order of ~5-10:1. Figure 2 shows a view of the trigger architecture.

This functional organization is mapped over three-categories of processor architectural organization. The L1 is implemented by a network of Field Programmable Gate Arrays (FPGA-s), and a network of Digital Signal Processors (DSP-s). The L2 and L3 is implemented over a network of commodity (general-purpose) workstations. The

FPGA-s are programmable, but are typically not dynamically loaded and adapted during runtime. Some limited fault-tolerant concepts can be applied in the FPGA hardware designs, but since deployment is relatively static, FPGA-s are currently considered outside the scope of the fault mitigation target.

## **DSP** Network

A network of Digital Signal Processors (DSP) is the primary computational engine for the L1 trigger. Chosen for their simple architecture, low-power and efficiency at low-level mathematical operations, the DSP-s must sustain high input data and processing rates, and operate with stringent real-time requirements. It has been estimated that ~2500 DSP-s are required. A DSP has minimal resources – 1 MB SRAM, and 64 MB DRAM – with no memory management facilities. To keep overhead to a minimum, a small microkernel provides a small set of facilities to the programmer. Communication facilities are also minimal. A point-to-point network allows transfer of data packets between processors. DMA co-processor assists the transfer over the communication ports and permit direct access of data from specialized I/O interfaces.

The DSP processor network is configured in application-specific topologies that optimize the aggregate system bandwidth. Since multiple communication ports are available per processor, the network can be tuned to increase bandwidth, or to support redundant pathways between processors.

A network of general purpose computers with roughly the same node count as the DSP subsystem is the primary computational engine for the L2/L3 trigger. The planned architecture leverages commodity processors implementing a large-scale Linux-based network. These nodes are connected via high-speed Ethernet interfaces, with multiple

interfaces in each permitting some fault resilience. Each node has more resources than a DSP-s, with large memory (~1 GB), storage, and runs a full-scale commodity operating system. In addition, the real-time requirements are much more relaxed than with the DSP-s. The nodes still have soft real-time requirements, but the deadlines are at least an order of magnitude greater

#### **Buffers and Switches**

A third component of the BTeV trigger architecture which is present across multiple levels are buffers and switches. The pixel data from the detectors is collated into packets and time-stamped, and are queued in a large buffer (L1 buffer). A demultiplexing switch delivers elements, which represents a single crossing's (collision) worth of data, from the queue to DSP-s in a round-robin fashion. The data is deleted from the L1 buffer if the trigger algorithm results in a reject decision; otherwise it is retained for further processing in the L2/3 trigger.

Given the scale of the BTeV Trigger system, a wide range of failures can be expected. Failures ranging from mechanical failures such as fans, cables; to electrical failures such as power supplies, voltage regulators; to processor hardware failures such as memory errors, communication link errors, processor and board failures; to software failures, such as algorithm bugs, are expected to occur. Moreover, the constraint of operating in proximity of a high radiation environment, with budget and technology limitations (radiation hardened processors are typically a generation behind their commonly available counterparts, and an order of magnitude greater in cost) precluding the use of radiation hardened devices, renders the system more vulnerable.

When failures do occur, they must be corrected very quickly. Otherwise the system will rapidly saturate the available queuing and start dropping potentially valuable experiment data. The loss of data in the event of a failure must be minimized and controlled. A highly coordinated fault mitigation mechanism is required that responds rapidly to failures, restoring the functionality in a short period of time thereby limiting the loss of experiment data. In the following section we describe the self-adaptive approach that rapidly adapts the system when failures occur retaining the system functionality, and in a longer time-scale re-optimizes the system to minimize the performance degradation.

### **Proposed Solution**

The system to support BTeV experiment is extremely large and expensive. Budget limitations preclude redundancy approaches to add robustness to the system such as the triple mode redundancy, or more than that. The physics community would not permit the "waste" of these resources, so any redundancy will be consumed with elective processing. The solution needs to be robust and cost effective. In this case a, fault mitigation approach is more desirable than traditional fault tolerance. Fault mitigation allows the system to adapt, giving a 'best-effort' behavior. The definition of 'best-effort' is application and mode specific.

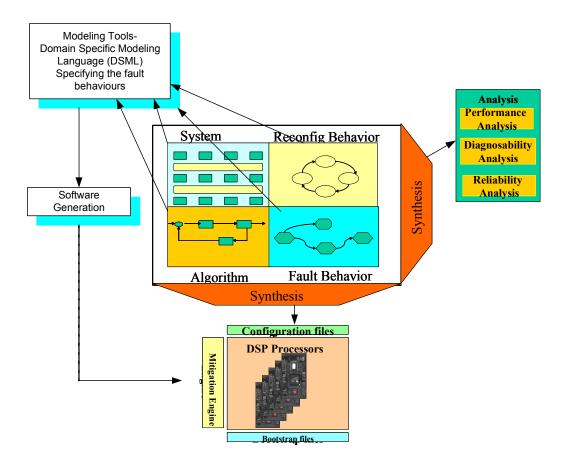

A proposed solution provided by the BTeV group at Fermi lab is shown in Figure 7 which shows the overall approach where the modeling tools provide the ability to define expected faults and corresponding fault mitigation actions. These actions can be analyzed and simulate the fault mitigation behaviors to assess the systems ability to respond to different failure scenarios. Analysis and simulation allows assessment without

having to create expensive test-beds and running exhaustive tests. Moreover, the tools have the ability to synthesize low-level programming artifacts from the higher-level abstractions, alleviating the system developer from the burden of constructing low-level artifacts and ensuring consistency with the higher-level abstractions.

With this motivation we have been developing high level design tools, and a highly matching flexible fault-tolerance runtime infrastructure. With this approach, the physicists – domain experts and users of the system – model the system using a domain-specific graphical language (DSL). Here they specify the hardware configuration, the software application and the fault-mitigation behaviors.

Figure 7 Model Based Approach to Fault-Mitigation

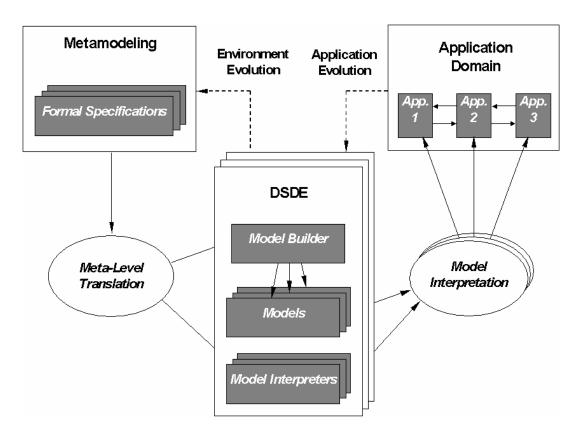

The DSL is implemented within the Generic Modeling Environment (GME) tool, which is a meta-programmable modeling environment, developed at the Institute of Software Integrated Systems ISIS, Vanderbilt University.

Model Integrated Computing (MIC) is a design philosophy that advocates the use of domain specific concepts to represent system design. The models capturing the design are then used to synthesize executable systems, perform analysis or drive simulations. The advantages of this methodology are that it speeds up the design process, facilitates evolution, helps in system maintenance and reduces the cost of the development cycle [14].

Figure 8 Design flow from metamodeling to application synthesis using GME

A metaprogrammable toolkit within Generic Modeling Environment (GME) implements the MIC methodology. It provides an environment for creating domainspecific modeling environments [11][14]. The GME metamodeling environment provides a graphical interface similar to UML [21] class diagrams (tutorial in appendix A), in which the user can specify the modeling environment to be developed for the specific domain. The graphical description is referred to as a metamodel. It captures the syntax, semantics and visualization rules of the target environment. In the metamodels the user can specify the set of entities or objects that can be created in the target environment, their organization and interactions with other entities. It also specifies associations, grouping and ordering of these objects. The target environment implements a modeling language, which allows the user to create any possible models consistent with the metamodel. A tool called the meta-interpreter interprets the metamodels and generates a configuration file for GME. The file is used to automatically configure GME so that it behaves like the target environment. Thus GME is used as both the metamodeling environment and the target environment.

GME models are entity relationship diagrams that are graphical and hierarchical with multiple aspects and attributes. The semantics of the models are enforced in two stages. The first stage is in the form of constraints that are applied to the models to enforce the static semantics. These constraints are specified in the metamodel using an Object Constraint Language (OCL) type specification and are applied on the models using a built-in constraint manager. In the second stage dynamic semantics are enforced by the model interpreters. Model interpreters parse the application models and generate source code, configuration files and analysis as output.

The key elements of an MIC-based approach in our application are:

- A Domain-specific modeling language (DSML), the syntax and static semantics

of which are precisely defined using UML-based notations and OCL-based

constraints in a meta-programming environment.

- 2. System developers build **Integrated multiple-view models** in the DSME capturing information relevant to the target system from several aspects. The information captured includes adaptive behaviors, information processing architecture, and physical architecture of the target system.

- 3. **Model translators**, generate inputs to various analysis tools, as well as synthesize various low-level artifacts for instantiating/deploying the system.

## **Summary**

Given the scale of the BTeV Trigger system, a wide range of failures ranging from mechanical failures such as fans, cables; to electrical failures such as power supplies, voltage regulators; to processing hardware failures such as memory errors, communication link errors, processor and board failures; are expected to occur. Moreover, the constraint of operating in proximity of a high radiation environment, with budget and technology limitations (radiation hardened processors are typically a generation behind their commonly available counterparts) precluding the use of radiation hardened devices, renders the system more vulnerable. The following summarizes the motivation behind handling such kind of systems.

- 1. When failures do occur, they must be corrected very quickly, or the system may rapidly saturate the available queuing and start dropping valuable experiment data.

- 2. The loss of data in the event of a failure must be minimized.

- 3. A highly coordinated fault mitigation mechanism is required that responds rapidly to failures, restoring the functionality in a short period of time thereby limiting the loss of experiment data.

- 4. Self-adaptive approach that rapidly adapts the system when failures occur to retain the system functionality, and in a longer time-scale re-optimizes the system to minimize the performance degradation.

#### CHAPTER IV

#### MODELING ENVIRONMENT

### Prototype Overview

In the previous chapter we presented an overview of the BTeV system. In this chapter we will discuss how we design, specify and implement the system using model based tools.

Prior to discussing the modeling tools we discuss a prototype software application that was implemented as a case study to simulate the L1 Trigger of the BTeV system.

The L1 trigger prototype contains several different software entities which are as follows:

- 1. *Generator*: simulates the behavior of the detector subsystem which is responsible for collating the pixel data from the detectors into time-stamped packets that are queued in a large buffer (L1Buffer).

- 2. **Buffer Manager**: simulates a large buffer of 120kb on each farmlet for queueing up events prior to processing.

- 3. *Switch*: mimics the behavior of a round robin network switch that distributes the incoming events from the L1 Buffer to the Buffer Managers It is a demultiplexing switch which delivers events, which is crossings worth of data, from the queue to Buffer Manager DSP's in a round robin fashion. The data is removed from the L1 buffer if the trigger algorithm results in a reject decision; otherwise it is retained for further processing in the L2/3 trigger.

- 4. *Workers*: are composed of processes which include the **Physics Application**(Trigger Application), **Detector** and the **Local Manager**. The *Physics*

Application (PA) grabs the events from the Buffer Manager and executes the trigger algorithm on the given event. The *Detector* is a fault detection process which monitors the occurrence of different types of faults including those in the Physics Application (ex: PA is stuck in a loop, event data errors, etc.). The Detector sends a message to the nearest Manager (Local Manager) to notify of the failures. The *Local Manager* acts a lowest level of Fault Manager, handling the faults in a user-defined manner.

The **Fault Managers** are synthesized from the modeling tools, using the user-specified fault mitigation behavior captured in the models. A highly coordinated fault mitigation mechanism is required that responds rapidly to failures, restoring the functionality in a short period of time thereby limiting the loss of experiment data.

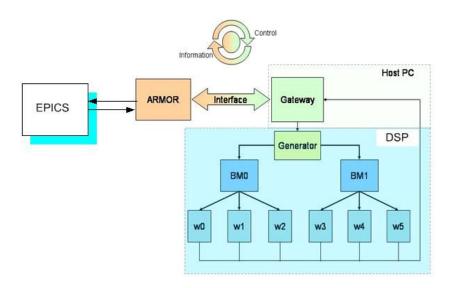

Figure 9 Prototype Software Application

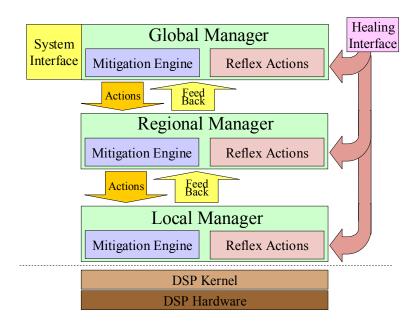

As shown in Figure 9 EPICS is the user interface and ARMOR is fault manager software – a product of UIUC [20]. In the BTeV application, we have defined three different hierarchical levels of control: local, regional, and global fault-managers. Hierarchy is a simple, yet powerful concept [32] that has been applied and proven in many types of complex and large-scale organization. Clearly, in a system of this size, sending all fault-information to a centralized fault-manager for a mitigation decision is not a scalable approach. Reaction time would suffer in small systems, and be increasingly large as systems are scaled up. We propose a hierarchical organization of fault-managers (FM) operating independently. Each FM has its individual control domains. FM coordinates with peers and parents/children, above/below outside their control domain. This improves the reaction time, and enhances scalability. Furthermore with distributed and coordinated decision making, a single-point failure of a centralized fault manager will not cause the entire system to fail.

The *Local* managers are the leaf nodes, responsible for sensing faults and implementing control actions and making low-level mitigation decisions. *Regional* managers handle successively larger regions of hardware and higher levels of mitigation behavior. There can be multiple levels or layers of regional manager. *Global* managers are the top-level fault mitigation agents, interfacing with external systems and/or users. These levels roughly correspond to the inherent hierarchical organization of the BTeV Trigger architecture.

Figure 10 Hierarchical Fault Mitigation Runtime Environment

Faults are handled at the lowest layer possible. At any specific level, if mitigation is not possible due to resource availability, or lack of sufficient contextual information, the fault is promoted to the next level of fault manager. This has the advantage of scaling, since the number of fault managers at the lower levels increases with the architecture size. In addition, response to a failure can be more rapid, since decisions are made closer to the source of error.

## **BTeV Paradigm**

### Mapping of Prototype into Modeling Environment

We now define a language to specify the Software /Hardware and the Fault Mitigation behavior of the target application. The meta-programmable tool GME implements a modeling environment with this graphical language. The goals of the

domain-specific graphical abstractions are to be are particularly natural to the physicists, amenable to analysis, and suitable for system synthesis. The BTeV modeling paradigm attempts to meet these goals by allowing for the specification of system from several different aspects. The significant aspects are:

- 1. Application **Data Flow**: the component-based specification of information processing to be performed by the system,

- 2. Hardware **Resources**: the physical computer hardware, consisting of processors and interconnections, used in system implementation, and

- 3. **Failure Mitigation Strategies**: the specification of how the system should detect and react to component and system failures.

These aspects will be described in detail below.

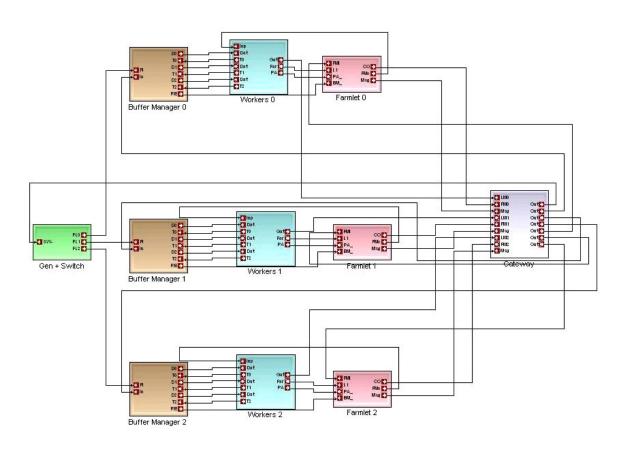

# Application Dataflow

This Application data flow aspect allows a system developer to define the key software components and the flow of data between them. The semantics are captured as a Dataflow Model, a modeling formalism, particularly suitable for modeling image and signal processing computations [37]. The basic dataflow model doesn't support hierarchical representation. However many extensions have been proposed that introduces hierarchy in the dataflow model [38]. Based on these extensions a hierarchical dataflow notation is used, where nodes (boxes) capture the software components (algorithms) and lines show the flow of data between nodes. Each of the software components are connected to each other by means of *Ports*. These models can represent synchronous or asynchronous behavior, and a variety of scheduling policies. For the BTeV trigger, these are primarily *asynchronous* in operation, with data-triggered

scheduling. The primitive software components represent a single computational block or algorithm to be executed in the runtime system. Each software primitive in the dataflow modeling are associated with a script that provides the implementation of the software component. Software Compounds are hierarchical composition of nodes. A Compound can contain other Primitives or Compounds. These data flow models are derived from those used in ACS-MIDE [19][24] and are made closely resemble a directed data flow graph [33].

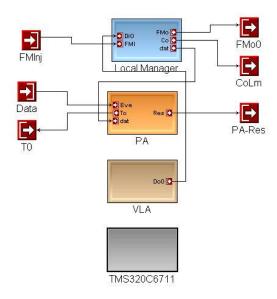

Figure 11 Software Component

Figure 11 shows a screen-shot of an example dataflow modeling aspect of the trigger prototype with several processes and dataflow links between them. The network of heterogeneous processing elements constitutes execution resource of the system. The set of computational components, the communication topology between the components, and the resource allocation together define the computational structure of the system. System configuration refers to computational structure of the system. Formally as mentioned in [24] the execution resources may be expressed as a set R of resources (processing elements) available for system execution.

Formally the computational structure of the system may be expressed as 3 tuple

$$\{P, F, A\} \tag{6}$$

where,

P is the set of computational processes (components)

$F \subseteq P \times P$  is the set of dataflow between processes and

A:  $P \rightarrow R$  is the resource allocation. Each process is assigned to a processing element.

The semantics of the computational structure can be described with an attributed directed graph know as process graph [37]. The nodes of the graph are computational processes. The edges of this graph represent communication (dataflow) between processes. Conceptually the processes operate continuously and concurrently transforming infinite sequence of input data to infinite sequence of output data. The processes communicate via exchange of data tokens. The communication is asynchronous and the tokens are buffered in FIFO queues. The processes in the process graph are distributed and executed over the set of resources R.

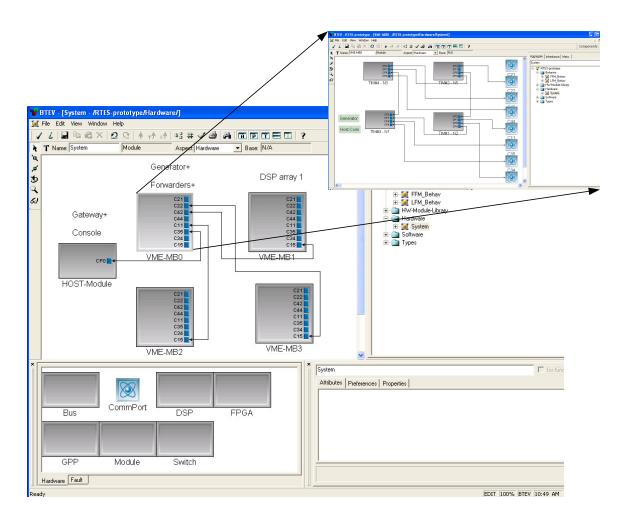

## Hardware Resource Library

This Hardware resource aspect defines the physical structure of the target architecture. Block diagrams capture the processing nodes (e.g. CPU-s, DSP-s, FPGA-s). Connections capture the networks and busses over which data can flow. These hardware resources provide the processing capabilities for executing software component currently modeled in the system. These hardware models are decomposed hierarchically to enable system scaling and support the use of types and instances to preserve the correctness of lower level hardware models.

Figure 12 Hardware Component

Figure 12 shows the segment of the hardware resource model for the prototype – 4 VME boards are wired to the host processor .Each VME board has maximum 4 DSP processors (TI TMSC6xxx).The hardware picture is arranged out the same way as the actual physical prototype hardware. The language for modeling the hardware component is again defined in UML.

#### CHAPTER V

#### FAULT MITIGATION LANGUAGE

As discussed previously about our approach towards mitigating the fault uses three level of hierarchy of fault managers operating independently with their own control domains and coordinating with peers outside their control domain. In this present chapter we will see the detailed explanation of the generation of these Fault- Manager behaviors from the models.

## Requirements

Historically physicists have developed custom software and hardware for experiments such as BTeV [15]. Any fault-mitigation would be manually programmed into the system. The motivation behind the fault mitigation strategy language is to provide a flexible method for specifying arbitrary mitigation behaviors. This tool provides for integration of prior knowledge into the fault detection system and the ability to use a recursive narrowing of fault probabilities to aid in the identification of symptoms. The goals of the fault mitigation language are as follows:

- 1. *User friendly*, keeping in mind that the target users are physicists

- 2. The language should be able to help the physicists introduce custom *self-adaptive* behaviors without any difficulty as they are the best people to define how the system should behave in fault conditions.

- 3. The language should integrate the application specification and design, since application is closely linked with the fault mitigation behavior.

4. It should support direct generation of software and system configuration artifacts from the specifications.

### <u>User Defined Mitigation Strategies</u>

State machine [4] based formal specification methodologies have found widespread acceptance in system design and development. This is especially true in the field of hardware /software Co-Design, since concepts of finite automata are often used to describe reactive system behavior. In addition to defining the normal system behavior, as in typical HW/SW codesign, we describe the *desired* behavior under fault conditions

One of the aspects of the BTeV modeling paradigm is the establishment of fault-mitigation strategy. A Statecharts-like [4] notation is provided that allows a developer to define various failure states. Conditions necessary to enter or leave these states, along with actions to be performed when state transitions occur are also defined in transitions. The language can be summarized at a high level as follows:

- 1. The nodes in the state diagram are system states, corresponding to a particular phase of system operation or a mitigation step.

- Lines are transitions between states, capturing the logical progression of system

modes. Transitions occur in reaction to specific events (i.e. hardware faults, OS

faults, user-defined errors, fault-mitigation commands from higher level of faultmanagers etc).

- 3. Transitions are annotated with triggers, guards and actions. Triggers determine the specific combination of events present when state transition should occur.

- 4. Actions define the operations to be performed as a transition occurs. These actions can include moving tasks, rerouting communications, resetting and

validating hardware and changing the application algorithms. An action language definition is currently being developed, and is left as future work.

The hierarchical mitigation scheme is specified by: 1) defining fault-managers to be executed at specific levels in the dataflow modeling hierarchy and 2) associating fault-mitigation strategies with each fault manager. In effect the fault-mitigation managers can be thought of as a system of concurrent and coordinating state-machines interacting via system state detectors data and event propagation.

The first step in the development of a new language is to specify the syntax and the visualization in the GME [14] -modeling environment. The meta-model for the state machine language uses a notation based on UML [21] class diagrams describing the key concepts of the modeling language and their associations. Figure 13 shows the metamodel of the fault mitigation language. It can be seen that *Behaviour* Component contains Machine which in turn contains the State. The Machine is the Fault Manager whose behavior can be described using StateChart concepts. Based upon whether they receive or send data the *Ports* can be specialized as *Input* or *Output*. The Behavior state machines perform actions based on triggering conditions. The *Triggers* is defined as a Connection which has attributes. These attributes specify the triggering condition and action to be performed. The action code which is the fault handling code is mainly written in C and based on the type of the guard/trigger. The action is user defined e.g. to send the message (action, error, statistical) upstream or downstream. These triggering conditions are logical equations using messages as inputs. Messages are utilized to propagate notification of failures up through the hierarchy, interact with fault detection processes, or communicate with other system components (e.g. user interfaces or system control).

Behavior Machine <<Folder>> <<Model>> SIBase <<FCO>> Transition <<Connection>> 0..1 Guard: State Trigger: field <<Model>> Action: field Decomposition : enum Initial <<Atom>> TypeConn <Connection>> dst 0..\* 0..\* TypeRefBase Data <<FCOProxy>> <<Atom>> ArraySize :field Scope: enum Modifier :enum Type: field InitialValue : field

Figure 13 State Machine paradigm

In order to minimize the bandwidth while providing the maximum flexibility, the messages are specified to have a variable length, based on the originator of the message.

## Message Structure

Considering the reactive and distributed nature of the system there is a need to send messages containing commands, status, and monitoring data back and forth between various software components in BTeV trigger systems. The messages defined for this prototype are:

1. Faults/Error Message for reporting errors in hardware, or application

- 2. *Controls/Command* serves as both decision requests and commands that force parameters to change in the running system

- 3. *Statistical/Info* is periodic in nature and they contain the data of averages over n time.

- 4. *Response Message* is feedback message which are sent when any kind of command or error messages are either executed or failed to execute.

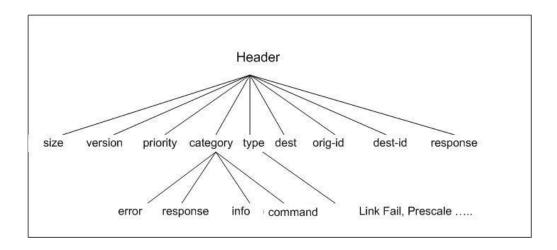

Figure 14 Message Structure

The above Figure 14 shows the message structure and the hierarchy of the message schema.

### Input and Output of the Fault Manager Machine

The state machine is an automaton whose state transitions may involve multiple input and output simultaneously on any number of ports. The key concepts here are the states (and in particular the transitions between them) and the interactions. By interactions we mean the explicit buffered communication via named *ports*. On each port

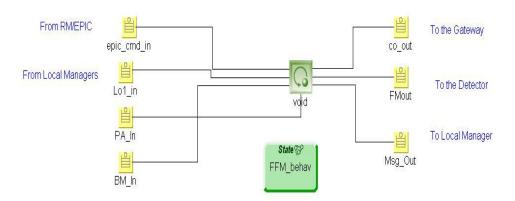

one receiver listens to potentially many senders. The input buffers are a set of message FIFOs. Message exchange is triggered by a state machine output within an Action specification or by other parts of computational environment. Inputs can be queued, i.e. they may occur at any time, appending the received value to the corresponding FIFO. The values in the input buffer will be processed based on the scheduling of the fault manager and its internal behavior. Processing is done by the user specified transitions, which is written in C language checks the type of message and uses it in a transition condition or guard. Based on the type of message the physicist can specify an action to be taken. This action would range from simply forwarding the message up the hierarchy to a parent fault manager, notification to another entity on the Fault Manger processor, updating an, activity log or internal state, restarting processes or hardware, or rerouting a communication link (if there is a link failure). Figure 15 shows the input and the output of the state machine.

Figure 15 Input and Output of State Machine

In order to use the system model described above, the messages and FSM definition is formally defined as follows:

Formally the messages can be expressed as:

Let M be the type of all messages potentially exchanged by the state machine (extended) and PN be the type of port names. Then the message families which are used to denote both input buffers and the output patterns have type

$$MSGs=PN\rightarrow M^*$$

(7)

where,

M\*is any finite sequence of elements of M.

**States and Transitions:** The type of a state is

$$STATE(\sum) = MSGs \ x \sum$$

(8)

where, the parameter  $\sum$  stands for the type of the local state. The set of transitions has type

TRANS

$$(\sum) = (STATE(\sum) \times MSGs \times STATE(\sum))$$

(9)

where, each of its elements has the form (( $i, \tau$ ),  $o, (i', \tau')$ ) and means that the state machine can perform a step from local state  $\tau$  to  $\tau'$ , taking the current input buffer contents from i to i' (thus consuming as much as input as required) and producing output o. Here i, i' and o each denote the whole families of FIFO's.

Formally, the Fault Managers behavior can be given as a 5 tuple:

$$(\mathbf{Q}, \mathbf{In}, \mathbf{Out}, \tau_{\theta}, \mathbf{Trans}(\mathbf{a})) \tag{10}$$

where,

- -Q is the set of finite states

- -*In* is the set of input ports names

- -Out is the set of output port names

- $\tau_0$  is the initial local state

- -Trans (a) is the transition relation

### <u>Various Features Of State – Machine Language</u>

Since the classic state machine doesn't handle hierarchy, extensions have been proposed to the FSM representation to introduce hierarchy and concurrency by Harel [4]. The main entities of the state machine are:

*State*: a particular condition in which a fault manager may consume signal /messages and evaluates conditions for transitions. The states are extended with two main concepts:

-State Hierarchy: The semantic of hierarchical state decomposition are designed to allow sharing of behavior